Serdes IP for GLOBALFOUNDRIES

Welcome to the ultimate

Serdes IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

Serdes IP

for

GLOBALFOUNDRIES

All offers in

Serdes IP

for

GLOBALFOUNDRIES

Filter

Compare

19

Serdes IP

for

GLOBALFOUNDRIES

from

11

vendors

(1

-

10)

-

32Gbps SerDes PHY in GF 22nm

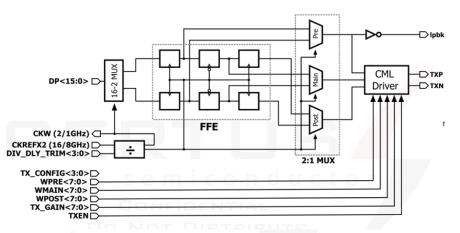

- This 32Gbps SerDes PHY is implemented in GlobalFoundries 22FDX CMOS technology and provides a high-performance, protocol-agnostic serial interface for advanced mixed-signal and high-speed digital SoCs.

- The PHY is architected as a modular design consisting of a low-jitter clock multiplier, a half-rate transmitter with digitally programmable feed-forward equalization, and a configurable CTLE-based receiver with digital clock-and-data recovery, supporting both 16 Gbps and 32 Gbps operation.

-

4.25 Gbps Multi-Standard SerDes

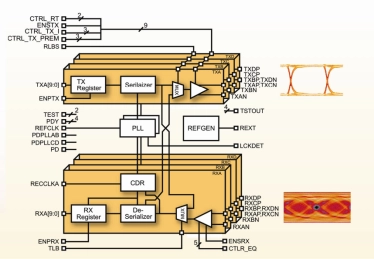

- The MXL4254A is a silicon proven Quad Gigabit SerDes implemented in digital CMOS technology. Each of the four channels supports data rate up to 4.25 Gbps.It is compatible with router-backplane links, PCI Express, SATA, RapidIO, 10 Gbps Ethernet (XAUI), FibreChannel, SFI-5, SPI-5, and other communication applications.

-

Ultra-short reach SerDes with 500 Gbit/s throughput

- 2x to 4x throughput at 50% or less energy consumption as compared to conventional SerDes over the same number of pins/wires

- High pin-efficiency and low power

- 208.3 Gbit/s full-duplex bandwidth per mm of die edge (500 Gbit/s for 2.4 mm of die edge)

-

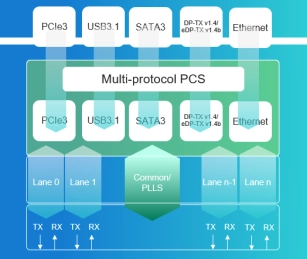

Ethernet SerDes - 16Gbps and 10Gbps multi-protocol SerDes PHY

- Wide range of protocols that support networking, HPC, and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- Extensive set of isolation, test modes, and loop-backs including APB and JTAG

- Supports 16-bit, 20-bit, and 32-bit PIPE and non-PIPE interfaces

- Selectable serial pin polarity reversal for both transmit and receive paths

-

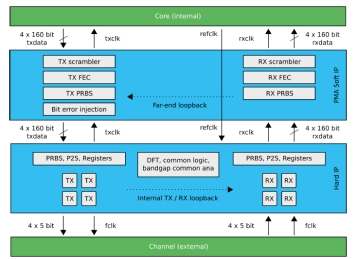

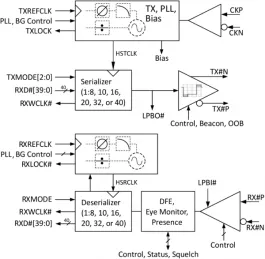

Multiprotocol SerDes PMA

- Supports over 30 protocols including CEI 6G & 11G SR, MR, LR, Ethernet 10GBASE-X/S/K/R, PCIe Gen1/2/3/4, V-by-One HS/US, CPRI, PON, OTN/OTU, 3GSDI, JESD204A/B/C, SATA1-3, XAUI, SGMII

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, or 40 bit

- Tx ring PLL includes fractional multiplication, spread spectrum and Jitter Cleaner function for Sync-E and OTU

- Core-voltage line driver with programmable pre-and post-emphasis

-

SerDes Hard Macro-IP in GlobalFoundries 22FDX

- Low-power, flexible and robust Serializer-de-serializer IP built upon a proven ring-PLL based architecture,

- Support for multiple protocols, as well as custom-designed SerDes to meet specific needs and wide range data rates

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, 40, 64, or 80 bit

- Easy integration; delivered including all supplies, ESD and RDL for your bump pitch

-

High Performance Transceiver

- Our FD-TRx Series is a transceiver comprising both of our breakthrough flagship FDDAC and FDADC technologies in a single chip offering a full solution for bi-directional connectivity.

- Its ultra-wide coherent modulation bandwidth and low energy consumption make it ideally suited for wide bandwidth applications such as mmWave-WiFi, mmWave5G and 6G, radar, or satellite.

-

High Speed Digital Interface

- High speed interfaces are key to establish communication between chips over varying distances.

- This ranges from ultra-short distances for chip-to-chip communication within a single package to a few centimetres to meters.

- Applications are for example establishing a data connection between a transceiver chip to a data source.

-

Multi-Standard SerDes PHY

- Configurable parallel data rate of 8 /10 / 16 / 20 / 32 / 40 / 64 / 80

- Input reference 5MHz to support 2.5/5/10G data rates

- Tight control over termination resistor (~50 Ohm) with on chip calibration

- Tight skew control of 1UI between lanes of the PMA

- Multi-tap Tx Finite Impulse Response (FIR) equalizer with multi-level de-emphasis

-

Custom Programmable Low Power SERDES on GLOBALFOUNDRIES 65G

- Programmable SERDES analog front end that supports 1 to 6+ Gbps standard serial protocols

- Compact form factor – 0.172 mm2 active silicon area per lane including ESD

- Industry leading low power – typically 11 mW/Gbps including termination

- Minimal latency – 3 UI between parallel transfer and serial transmission