Finite Impulse Response IP

Welcome to the ultimate Finite Impulse Response IP hub! Explore our vast directory of Finite Impulse Response IP

All offers in

Finite Impulse Response IP

Filter

Compare

17

Finite Impulse Response IP

from

9

vendors

(1

-

10)

-

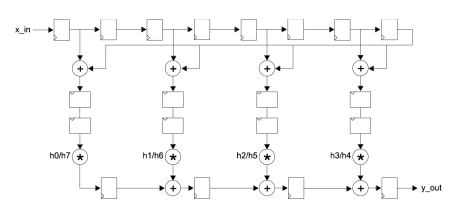

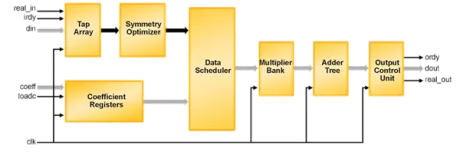

Generic high-speed FIR Filter with symmetry

- FIR filter designed for high sample rate applications with symmetrical coefficients and an even or odd number of taps.

- Features configurable coefficients and data width. Design uses only half the number of multipliers compared to a normal FIR implementation.

- Matlab®, FDAtool and Simulink® compatible.

-

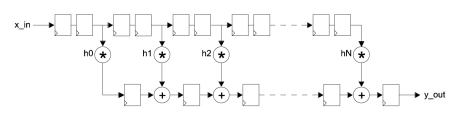

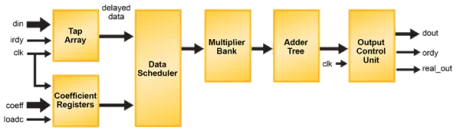

Generic ultra-speed FIR Filter

- FIR filter designed for very high sample rate applications up to 600 MHz.

- Organized as a systolic array, the filter is modular and scalable, permitting the user to specify large order filters without compromising maximum attainable clock-speed. Matlab®, FDAtool and Simulink® compatible.

-

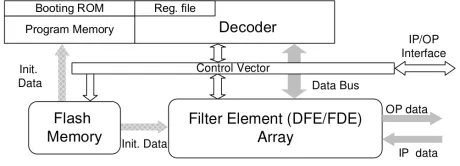

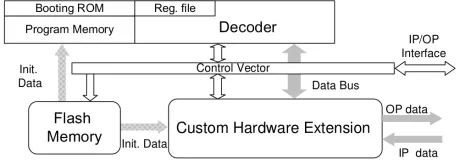

ASIP-1 FFT Engine

- Platform to design Application Specific Instruction Set Processors (ASIPs).

- Ideal for supporting multi-standard systems.

- Supports a wide range of complex DSP functions.

-

ASIP-2 Programmable Filter Engine

- Platform to design Application Specific Instruction Set Processors (ASIPs).

- Ideal for supporting multi-standard systems.

- Supports a wide range of complex DSP functions

- The ASIP2 performs Fast Fourier Transform (FFT) to convert time domain signals to frequency domain signals for further processing. It supports FFT sizes from 4 to 8K.

-

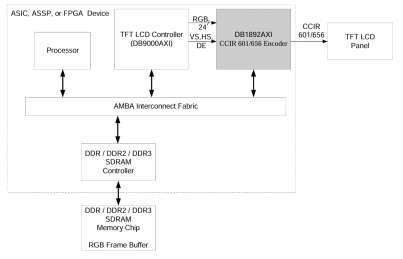

RGB to ITU-R 601/656 Encoder

- The DB1892AXI RGB to CCIR 601 / CCIR 656 Encoder interfaces RGB data along with synchronization signals from a LCD Controller (or any LCD display timing & control unit) to a TFT LCD Panel by-way-of a CCIR 601 / CCIR 656 interface.

-

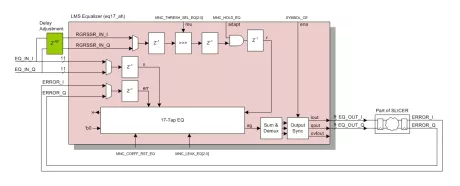

LMS Adaptive Channel Equalizer

- 17-tap T-spaced complex-arithmetic LMS signed-error Channel Equalizer

- Adaptation bandwidth control (mu, step size)

-

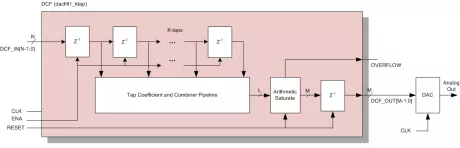

DAC Correction Filter

- Efficient, multiplier-free design

- Configurable input and output widths

- Multiple tap-length configurations

-

Serial FIR Filter

- Serial Arithmetic for Reduced Resource Utilization

- Variable Number of Taps up to 64

- Data and Coefficients up to 32 Bits

- Output Size Consistent with Data Size

-

Parallel FIR Filter

- Variable number of taps up to 64

- Data and coefficients up to 32 bits

- Output size consistent with data size

- Zero-latency operation

-

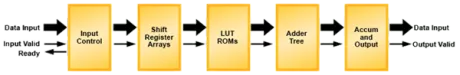

Distributed Arithmetic FIR (DA-FIR) Filter Generator

- Variable number of taps up to 1024

- Multi-channel support (up to 32 channels)

- Polyphase interpolation/decimation filters

- Halfband filters