065TSMC_PLL_08 is an integer-N phase-locked loop frequency synthesizer (PLL) based on fully integrated wide band LC-VCO with range from 3 GHz to 6 GHz with good phase noise performance. It works with

reference frequency from 25 MHz XTAL oscillator or external signal source with frequency up to 500 MHz. Phase-frequency divider compare frequency can be equal or 2,3,4...63 times lower than reference. VCO frequency N-divider has programmable coefficient of division with step 1 in range 4 to 2047. Phase-frequency detector has built-in analog and digital lock detector circuits. Charge pump scheme with ADC and adjustable output current allow compensation VCO gain variation within band and keep loop gain constant. Integrated low-pass loop filter has adjustable values of resistance and capacitance for tune loop and get best phase-noise performance.

The PLL is designed using TSMC 65 nm CRN65LP technology.

Wide band 3Ghz-6GHz integer phase-locked loop

Overview

Key Features

- TSMC CMOS 65 nm

- Integer-N phase-locked loop

- Wide frequency range from 3 GHz to 6 GHz

- Good phase noise perfomance

- Fully integrated VCO

- Fully integrated loop filter with ability to use external loop filter

- Built-in lock detection circuit

- High reference frequency spurious rejection

- Adjustable value of charge pump output current

- Built-in ADC for measuring VCO control voltage value

- Digital loop gain compensation

- Low current consumption

- Adjustable power supply voltage

- Portable to other technologies (upon request)

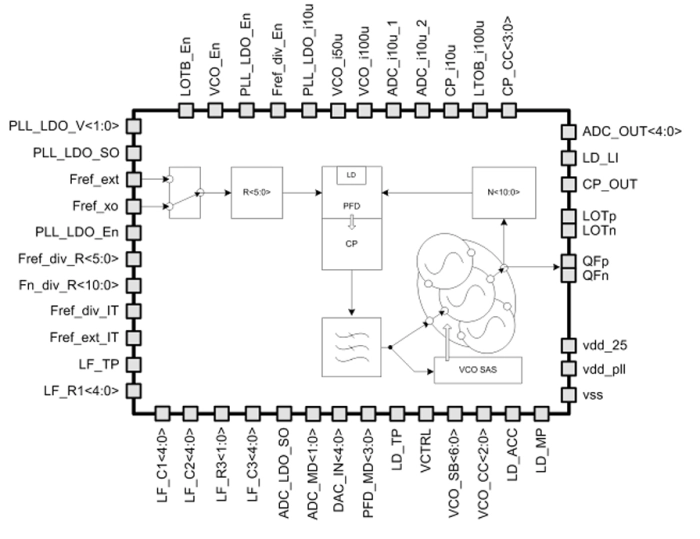

Block Diagram

Applications

- RF receivers, transmitters, transceivers

- High frequency clock generation

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

Wide band 3Ghz-6GHz integer phase-locked loop

Vendor

Vendor Name

Foundry, Node

TSMC CMOS 65 nm

Maturity

silicon proven

Availability

Now

TSMC

Silicon Proven:

65nm

G