Phase-locked loop clock generator

It is a integer-N phase-locked loop frequency synthesizer (PLL) based on fully integrated 2GHz LC-VCO with low gain and fine phas…

Overview

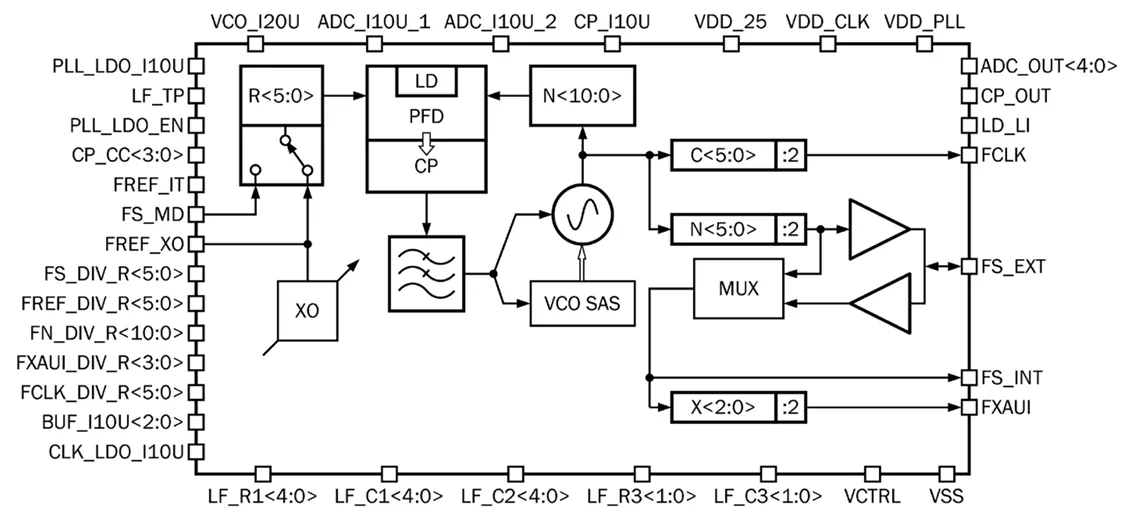

It is a integer-N phase-locked loop frequency synthesizer (PLL) based on fully integrated 2GHz LC-VCO with low gain and fine phase noise performance. It work with reference frequency from 25 MHz XTAL oscillator or external signal source with frequency up to 500 MHz. Phase-frequency divider compare frequency can be equal or 2,3,4...63 times lower than reference. VCO frequency N-divider has programmable coefficient of division with step 1 in range 4 to 2047. Phase-frequency detector has built-in analog and digital lock detector circuits. Charge pump scheme with ADC and adjustable output current allow compensation VCO gain variation within band and keep loop gain constant. Integrated low-pass loop filter has adjustable values of resistance and capacitance for tune loop and get best phase-noise performance. All of output clocks have 0.5 duty cycle value using duty cycle recovery circuit.

The QF is designed using TSMC 65nm CRN65LP technology.

Key features

- TSMC CMOS 65 nm

- Low phase noise

- Fully integrated 2 GHz VCO

- Fully integrated loop filter with ability to use external loop filter.

- Built-in lock detection circuit

- High reference frequency spur rejection

- Adjustable value of charge pump output current

- Built-in ADC for measuring VCO control voltage value

- Digital loop gain compensation

- Low current consumption

- Adjustable power supply voltage

- Portable to other technologies (upon request)

Block Diagram

Applications

- Low jitter clock generation

What’s Included?

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 65nm | GP | Silicon Proven |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Clock Generator IP core

Enhance circuit timing design with programmable clock generators (Part 1 of 2)

M31 on the Specification and Development of MIPI Physical Layer

Silicon-Accurate Fractional-N PLL Design

FPGA Implementation of DLX Microprocessor With WISHBONE SoC Bus

Mixed Signal Drivers for Ultra Low Power and Very High Power Applications

Frequently asked questions about Clock Generator IP cores

What is Phase-locked loop clock generator?

Phase-locked loop clock generator is a Clock Generator IP core from NTLab listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Clock Generator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Clock Generator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.