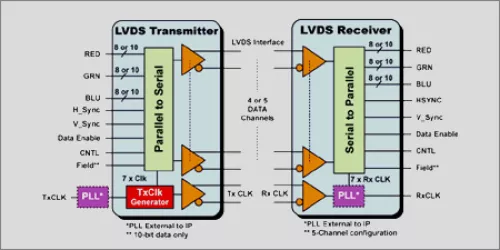

The Video LVDS SerDes Transmitter / Receiver IP Core provides a complete, easy-to-use Serializer/Deserializer (SerDes) solution to interface a wide variety of video host systems to Flat Panel displays. The core simplifies the design of video LVDS interfaces, improves data integrity and timing margins. For example, the Transmitter has the ability to generate an LVDS transmit clock synchronous to the video data stream thereby eliminating the need to fine-tune a PLL to the outputted LVDS data. Similarly, the Receiver auto aligns the receive clock to the encoded video to assure data synchronization. An easy to use GUI enables the user to select the number of LVDS links and to configure the number of data channels for each link.

The Transmitter and Receiver cores support both 28 bit (8 bit RGB) and 35 bit (10-bit RGB) parallel data configurations using either 4 or 5 LVDS serial channels. Transmitter and Receiver modules can be cascaded to create dual and quad LVDS links supporting display panel resolutions up to 1080p at 120 Hz and beyond.

Video LVDS SerDes Transmitter-Receiver IP Core

Overview

Key Features

- 7:1 Serializer/Deserializer (SerDes)

- Optimized for 8 and 10-bit HD video applications

- Supports both 28-bit and 35-bit parallel data (mapped into 4 / 5 LVDS channels)

- Supports Flat Panel resolutions up to 1080p 120Hz and beyond

- Cascade modules to support Dual & Quad LVDS link configurations

- LVDS TxClock phase aligned to encoded data, no PLL fine tuning required

- Receiver auto aligns clock to encoded video data from input LVDS data stream

- Configuration GUI streamlines design process

- Complies with Open LDI Specification for Digital Display Interfaces

- Supports Cyclone II, III, IV, Stratix III & IV, and Arria family of devices

Benefits

- The Video LVDS SerDes Transmitter / Receiver IP Core is specifically targeted at high-performance video applications including; flat panel displays, HDTV consumer electronics, video display resolution conversion / enhancement equipment, automotive navigation/DVD entertainment systems, camera link devices, and high-speed interconnects.

Block Diagram

Deliverables

- ModelSim/VHDL precompiled simulations library

- Includes license and 1 year of updates

- Reference designs

- Altera OpenCore Plus evaluation

Technical Specifications

Short description

Video LVDS SerDes Transmitter-Receiver IP Core

Vendor

Vendor Name

Availability

Available for immediate sale