The Arasan USB 2.0 OTG IP Core is compliant with the OTG Supplement Rev. 1.0a. The USB 2.0 OTG core supports both Host Controller, Device Controller and OTG functionality. When operating as a host (A-device), it supports 480 Mbit/s in High Speed (HS) mode, 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode. When operating as a peripheral (B-device), it supports HS and FS modes.

Session Request Protocol (SRP) and Host Negotiation Protocol (HNP) are managed by the SRP/HNP Control Logic. SRP allows a B-device to request an A-device to turn on Vbus to start a session. HNP allows two connected dual-role devices to change roles and eliminates the needs for the user to switch cable connections. The Vbus Control Circuit supports: a) the generation of data-line pulsing and Vbus pulsing methods when initiating the SRP as a Bdevice, b) the detection of both pulsing methods when acting as an A-device, and c) the sourcing of a minimum of 8 mA on Vbus. The Vbus Control Circuit also handles the pull-up and pull-down connections to D+ and D- during host/device role switching. The SRP/HNP Logic and Vbus Control Circuit control the operating mode of an USB port as either a host or peripheral. The Arasan USB 2.0 OTG port requires an external USB 2.0 transceiver with a standard UTMI interface.

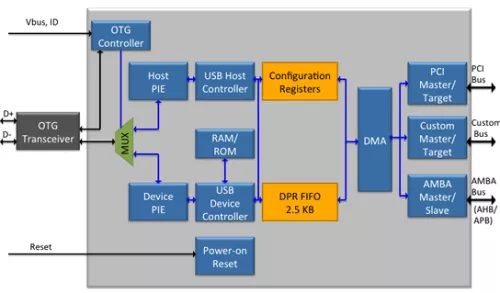

The Arasan USB 2.0 OTG IP Core offers a high level of flexibility, allowing designers to implement the USB 2.0 OTG port with a wide selection of processor interfaces. AHB, PCI, and Custom buses are available to provide a high-speed connection to the USB interface.

The Arasan USB 2.0 OTG IP Core is augmented by the availability of the Arasan OTG Software Stack that supports host driver, device driver, class of devices, and Linux operating system.

USB 2.0 On-The-Go Controller

Overview

Key Features

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

- Master DMA implementation for each endpoint

- Optional PIO Mode for each endpoint (can be used for Interrupt endoints)

- System bus Master/Target clock

- UTMI Interface Clock: 30/60 MHz

- Endpoint Configuration

- Configurable up to 15 Tx and Rx endpoints

- Configuration options: Bulk, control, isochronous, interrupt

- Dedicated control endpoint zero

- Configurable dual port RAM shared between endpoints

- USB Suspend/Resume support

- 32/64 bit AXI, AHB or OCP bus interfaces

Benefits

- Fully compliant to USB 2.0 specifications

- Highly flexible and configurable

- Ideal for easy and cost-effective device integration

- Premier direct support from Arasan IP Engineering Team

Block Diagram

Deliverables

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

- Simulation scripts

Technical Specifications

Maturity

Silicon Proven

Availability

Now