FlexCAN Controller for CAN 2.0 with CAN-FD

The FlexCAN controller is a configurable, synthesizable core implementing the CAN protocol (ISO 11898-1), CAN with Flexible Data …

Overview

The FlexCAN controller is a highly configurable, synthesizable core implementing the CAN protocol (ISO 11898-1), CAN with Flexible Data rate (CAN FD), and CAN 2.0 B protocol specifications, built from silicon-proven technology.

Key features

- Full implementation of CAN FD and CAN 2.0 B

- Standard/extended data frames

- Up to 8Mbit/s

- 0-64 bytes data length

- Compliant with ISO 11898-1

- Flexible mailboxes configurable

- To store 0-8, 16, 32, or 64 data bytes

- As receive or transmit

- Individual Rx mask register per mailbox

- Full featured Rx FIFO, stores up to 6 frames

- Transmission abort capability

- Listen-only mode

- Loop-back mode supporting self-test operation

- Programmable transmission priority scheme

- Time stamp based on 16-bit free-running timer with an optional external time tick

- Low power modes with programmable wake-up on bus activity or matching with received frames (pretended networking)

- Transceiver delay compensation for CAN FD Tx at faster data rates

- Detection and correction of memory read (ECC)

- SystemVerilog integration testbench including a number of usage scenarios

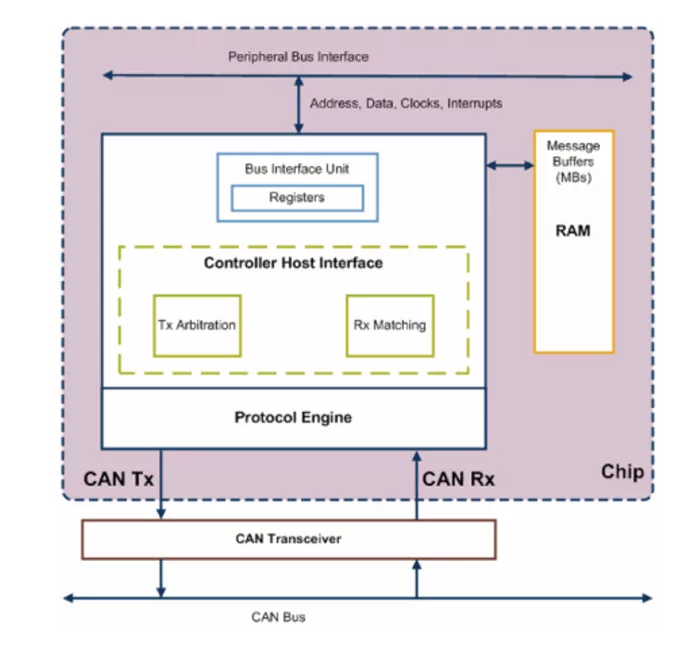

Block Diagram

What’s Included?

- Verilog RTL source code

- Test bench with test suites

- Documentation including User's Guide and Integration Guide

- Technology-independent synthesis constraints

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CAN / CAN-FD / CAN-XL IP core

Fraunhofer/CAST CAN XL IP Core Succeeds in First Multi-Vendor Plugfest

Frequently asked questions about CAN / CAN FD / CAN XL IP cores

What is FlexCAN Controller for CAN 2.0 with CAN-FD?

FlexCAN Controller for CAN 2.0 with CAN-FD is a CAN / CAN-FD / CAN-XL IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this CAN / CAN-FD / CAN-XL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CAN / CAN-FD / CAN-XL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.