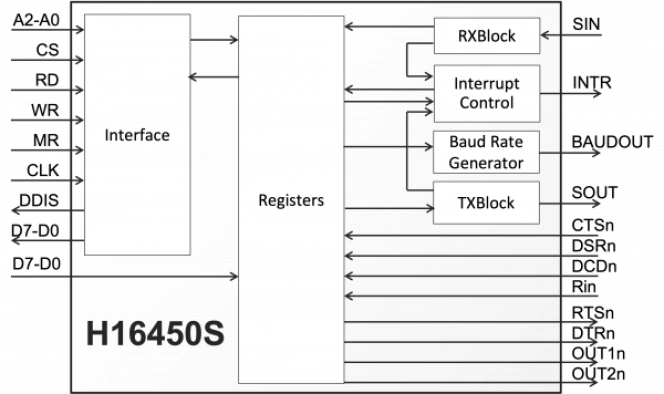

The H16450S is a standard UART providing 100% software compatibility with the popular Texas Instruments 16450 device. It performs serial-to-parallel conversion on data originating from modems or other serial devices, and performs parallel-to-serial conversion on data from a CPU to these devices.

Developed for easy reuse in ASIC and FPGA applications, the H16450S is available optimized for several technologies with competitive utilization and performance characteristics.