UART Serial Interface Controller

Overview

The CC-UART-AXI is a synthesisable Verilog model of a UART serial interface controller. The UART core can be efficiently implemented on FPGA and ASIC technologies.

Key Features

- UART-compatible interface

- AMBA AXI4-Lite bus

- Full duplex

- Custom baud rate generation

- 8x, 16x oversampling

- 5, 6, 7, 8, 9 bits data

- 1, 2 stop bits

- LSB or MSB mode

- Configurable parity

- Hardware flow control

- RS485 mode

- Maskable interrupts

- Dedicated upstream and downstream DMA interface

- Fully synthesizable synchronous design with positive edge clocking

- DFT ready

Benefits

- Synthesizable RTL Verilog source code

- Technology independent IP Core

- Suitable for FPGA and ASIC

- Silicon and FPGA proven

- Easy SoC integration

- Full implementation and maintenance support with individual approach

- Flexible licensing scheme

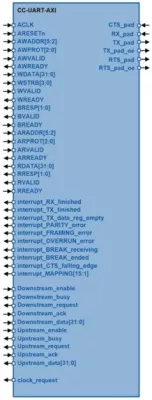

Block Diagram

Deliverables

- Verilog RTL source code

- Verification suite

- Datasheet and integration guide

- C-header file

- Constraints

- Technical support

Technical Specifications

Short description

UART Serial Interface Controller

Vendor

Vendor Name

Related IPs

- UART with Synchronous CPU Interface

- UART with FIFOs and Synchronous CPU Interface

- UART with FIFOs, IrDA and Synchronous CPU Interface

- Serial Peripheral Interface (SPI) Master Module

- SpaceWire link controller with SpaceWire RMAP support and AMBA host interface

- 10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface