The Serial Lite IV Intel® FPGA Intellectual Property (IP) core is suitable for high-bandwidth data communication for chip-to-chip, board-to-board, and backplane applications.

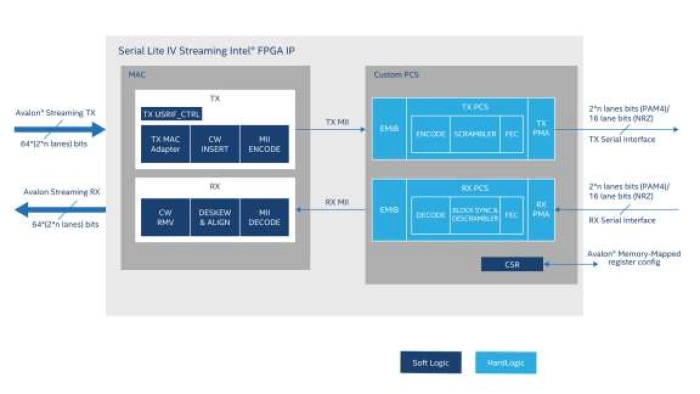

Serial Lite IV IP core incorporates a media access control (MAC), physical coding sublayer (PCS), and physical media attachment (PMA) block. The IP supports data transfer up to 58 Gbps per lane with a maximum of 12 PAM4 lanes of the Intel® Agilex™ 7 F-tile General-Purpose Transceivers (FGT) and up to 116 Gbps with a maximum of 4 PAM4 lanes of the Intel® Agilex™ 7 F-tile High-Speed Transceivers (FHT) in a single link or 28 Gbps per lane with a maximum of 16 non-return-to-zero (NRZ) lanes of FGT and 58 Gbps per lane with a maximum of 4 NRZ lanes of FHT. This protocol offers high bandwidth, low overhead frames, and low I/O count supporting high scalability in both numbers of lanes and speed. The IP is easily reconfigurable with support of a wide range of data rates with Ethernet PCS mode of the E-Tile transceiver and the F-Tile transceiver with our latest GTS transceivers for the Agilex™ 5 devices.

This IP supports two transmission modes:

- Basic mode—This is a pure streaming mode where data is sent without the start-of-packet, empty cycle, and end-of-packet to increase bandwidth. The IP takes the first valid data as the start of a burst.

- Full mode—This is the packet mode of data transfer. A burst and sync cycle is sent at the start and at the end of a packet as delimiters.

Features

| Feature | Description |

|---|---|

| Data Transfer |

|

| PCS |

|

| Error Detection and Handling |

|

| Interfaces |

|