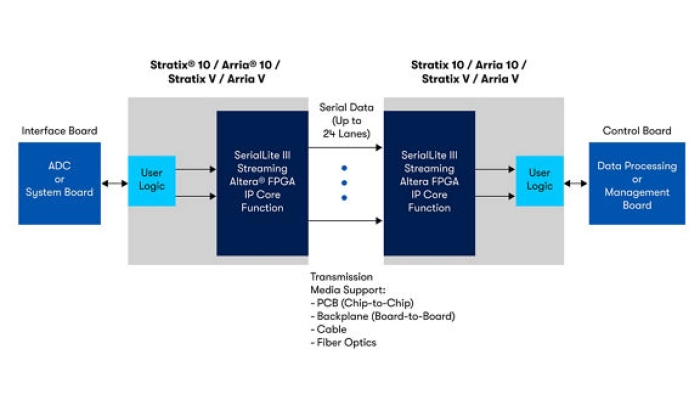

The Serial Lite III Streaming Intel® FPGA Intellectual Property (IP) core offers simple connectivity that enables rapid point-to-point data transfers across various transmission media, including printed circuit board (PCB), backplane, copper cabling, and fiber optics.

Serial Lite III is a simple, low-latency, scalable protocol for high-bandwidth serial data transfer applications.

The Serial Lite III Streaming Intel® FPGA IP core includes Intel’s technology-leading transceivers:

- Physical medium attachment (PMA)

- Physical coding sublayer (PCS)

- Media access control (MAC) layers

The PCS and PMA layers are hardened within the Intel Stratix® 10, Intel Arria® 10, Stratix® V, and Arria® V FPGAs to save customers valuable FPGA logic resources.

The hardened PCS/PMA functionality enables much easier timing closure for all types of designs. The Serial Lite III protocol was designed to provide the necessary reliability, low latency, overhead, and scalability to ensure efficient data transfers and maintain low bit error rates required by today’s and next-generation systems.

Performance and Productivity You Can Expect

|

Performance |

Productivity |

|---|---|

|

High data rate efficiency |

Adequate IP timing margin to accelerate full design timing closure |

|

Over 300 Gbps of aggregate bandwidth for current and emerging applications (up to 24 lanes) |

Intel FPGA IP Evaluation Mode feature allows you to test drive IP for free and without a license |

|

Low-latency data transfers (< 150 ns: TX + RX) |

Fully integrated Serial Lite III IP includes MAC, PCS, and PMA layers for ease of Intel FPGA IP integration |

|

AC and DC coupling allows flexibility to tune lane(s) for improved bit error rates |