The SD 4.1/SDIO 4.1 IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports two key memory card I/O technologies:

SD 4.1

SDIO 4.1

SD 4.1 Host Controller IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds. The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC memory, thereby simplifying system initialization during power up. The SD 4.1 Host interface is based on a standard 32-bit AXI bus which is used to transfer data and configure the IP.

SD 4.1 SDIO 4.1 Host Controller IP

Overview

Key Features

- Compliance

- Compliant with Part A2 SD Host controller Version 4.00

- Compliant with Part 1 Physical Layer specification Version 4.00

- Compliant with Part 1 SD specifications UHS-II addendum Ver1.00

- Compliant with Part A2 SD Host controller Version 3.01

- Compliant with Part 1 Physical Layer Specification Version 3.01

- Compliant with Part E1 SDIO specification Version 3.00

- Compliant with eMMC Specification Version 5.0

- AMBA AXI Specification Version 3.00 (Standard)

- AMBA AHB Specification Version 2.00 (Optional)

- OCP specification Version 2.2 (Optional)

- Core Features

- Supports one of the following System/Host Interfaces: AHB, AXI or OCP

- Data transfer using PIO mode on the Host Bus Slave interface, using DMA mode on the Host Bus Master interface. Here the Host Bus is AHB or AXI or OCP Interface

- Supports eMMC5.0 Security Protocol Commands

- Supports 32-bit and 64-bit system bus

- Configurable FIFO size to support different block sizes

- Supports Interrupts and wake up functionality

- Supports Internal Clock divider for various card operational modes

- UHS-II Features

- Supports UHS-II data transfer rates between 390Mb/s to 1.56Gb/s

- Supports Full duplex & Half duplex modes

- Supports peak interface speed of 3.12 Gb/s in Half-duplex; 1.56 Gb/s in Full-duplex mode

- Multiple power saving modes: Dormant, Line standby

- Interface speed is continuously variable

- Interfaces to Arasan’s UHS-II PHY Analog Front End

- Implements UHS-II Digital PHY Interface, Link Layer, Transaction Layer and Legacy SD3.0 functionality

- Supports Point to Point for Single UHS-II device and Ring topology for supporting Multiple UHS-II devices

- Card Detection (Insertion / Removal)

- Auto detects UHS-II and UHS-I cards

- UHS- I Features (SD3.0/SDIO3.0)

- Host clock rate variable between 0 and 208 MHz

- Up to 832Mbits per second data rate using 4 parallel data lines (SDR104 mode)

- Transfers the data in 1-bit and 4-bit SD modes and SPI mode

- Transfers the data in SDR104, DDR50, SDR50, SDR25, SDR12, DS & HS modes

- Supports 1.8V voltage Switch operation

- Supports Tuning for SDR104 and SDR50

- Cyclic Redundancy Check CRC7 for command and CRC16 for data integrity

- Variable-length data transfers

- Performs Read wait Control, Suspend/Resume operation SDIO CARD

- Designed to work with I/O cards, Read-only cards and Read/Write cards

- Supports Read wait Control, Suspend/Resume operation

- Card Detection (Insertion / Removal)

Benefits

- Fully compliant, silicon-proven core

- Premier direct support from Arasan IP core designers

- Easy-to-use industry standard test environment

- Unencrypted source code allows easy implementation

- Reuse Methodology Manual guidelines (RMM) compliant verilog code ensured using Spyglass

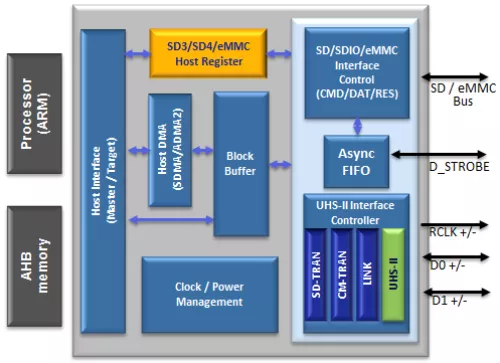

Block Diagram

Deliverables

- Verilog HDL of the IP Core

- User guide

- Test Environment and test scripts

- Synthesis scripts

Technical Specifications

Maturity

Silicon Proven

Availability

Now