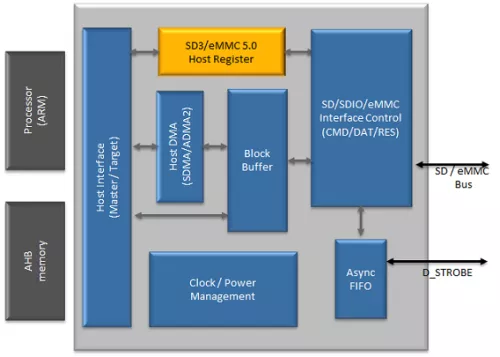

Arasan Chip Systems’ eMMC 5.0 / SD3.0 Host Controller IP (3MCR) is a highly integrated host controller IP solution that supports three key memory and I/O technologies: 1) SD, 2) SDIO and 3) eMMC memory formats. This IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.

The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC memory, thereby simplifying system initialization during power up. The host interface is based on a standard 32-bit AHB bus which is used to transfer data and configure the IP.

Arasan’s thorough verification methodology takes the risk out of integration of this functionality. As an Executive Member of the SD Association and JEDEC eMMC committee, Arasan is a leading provider of quality IP ensuring SoC designers risk-free integration of this advanced functionality. In addition to providing the Three Function MCR IP core, Arasan provides a family of different memory solutions to address a variety of needs. Arasan provides verification IP, test environment and a hardware development kit to ease integration into an SoC.

SD 3.0 / SDIO 3.0 / eMMC 5.0 Host Controller

Overview

Key Features

- Memory Card / Form Factors:

- SD Host Controller Spec v3.0* (SDXC)

- SDIO Spec v3.0

- SD Memory Spec v3.01

- eSD Memory Spec v2.1

- eMMC Spec v5.0

- IP Details:

- Built-in Master DMA for efficient data transfer

- Supports single slot

- SD - Secure Digital Memory Card

- 25/50/104/208 MHz

- 1,4 bit of data

- SDIO - SD Input/Output

- 25/50/104/208 MHz

- 1,4 bit of data

- eMMC -

- 26/52/208 MHz

- 1,4,8 bit of data

- HS200, HS400

Benefits

- Fully compliant core with proven silicon

- Premier direct support from Arasan IP core designers

- Easy-to-use industry standard test environment

- Unencrypted source code allows easy implementation

- Reuse Methodology Manual guidelines (RMM) compliant verilog code ensured using Spyglass

Block Diagram

Video

Arasan eMMC 5.0 Host Controller Hardware Validation Platform Demonstration

Arasan eMMC 5.0 Host Controller Hardware Validation Platform Demonstration

Deliverables

- RMM Compliant Synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

Technical Specifications

Maturity

Pre-silicon

Availability

Now