Direct Memory Access (DMA) is a technique for transferring blocks of data between system memory and peripherals without a processor (e.g., system CPU) having to be involved in each transfer. DMA not only offloads a system’s processing elements, but can transfer data at much higher rates than processor reads and writes.

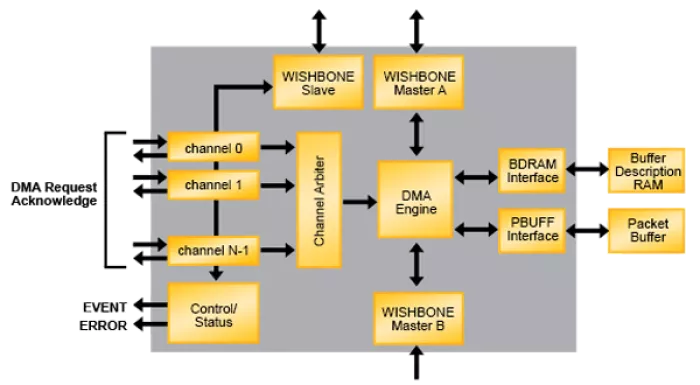

Scatter-Gather DMA augments this technique by providing data transfers from one non-contiguous block of memory to another by means of a series of smaller contiguous-block transfers. The Lattice Scatter-Gather DMA Controller core implements a configurable, multi-channel, WISHBONE-compliant DMA controller with scatter-gather capability.

Scatter-Gather DMA Controller

Overview

Key Features

- Supports up to 16 physical channels

- Up to 8 sub-channels per physical channel

- Four priority levels using round-robin arbitration (weighted or simple)

- WISHBONE bus widths from 8 to 128 bits

- Simple DMA, split transfers, scatter-gather

- Direct interface to external RAM for packet buffering

- Autonomous and hardware-directed retry

- Supports WISHBONE burst and classic-cycle transfers

- Supports centralized and distributed DMA control architectures

Block Diagram

Technical Specifications

Short description

Scatter-Gather DMA Controller

Vendor

Vendor Name