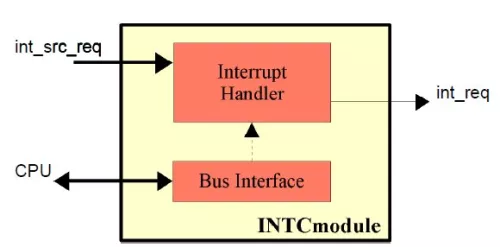

This interrupt controller can be used to bundle several different interrupt sources into one main system interrupt.

The interrupt controller provides an enable register for each source request. The interrupt status register displays the current pending interrupts, the masked status register shows the status of all enabled interrupt sources. Each pending interrupt can be acknowledged individually without affecting any other interrupts. This features helps to avoid situations where a new interrupt happens while the CPU is in the middle of the interrupt service routine.

Programmable Interrupt Controller

Overview

Key Features

- Up to 32 different interrupt sources

- Individual interrupt acknowledgement

- Individual interrupt status register

- Masked interrupt status register

- Supports synchronous bus interfaces such as AMBA APB version 2.0

- Full synchronous design

- Synthesis options:

- CPU readback enable

- Number of interrupt sources

Benefits

- For gate-count optimization, the core can be configured to disable the configuration register read-back path. Synthesis options are included to use the core in 8, 16 and 32-bit systems. With a separate APB wrapper, the core can be used in ARM subsystems.

Block Diagram

Applications

- Industrial control

- System-on-Chip

- Peripheral logic

- Embedded systems

- CPU subsystems

Deliverables

- VHDL or Verilog RTL Source Code

- Functional Testbench

- Synthesys Script

- Data Sheet

- User Guide

- Hotline Support by means of phone, fax and e-mail

Technical Specifications

Foundry, Node

Technology independent

Maturity

Proven in ASIC and FPGA Technologies

Availability

now