The MXL_MPHY_S_090LL is a high-frequency low-power, low-cost, Physical Layer IP that supports the MIPI Alliance Standard for M-PHY. The IP can be used as a physical layer for many applications, including interfaces for display, camera, audio, video, memory, power management and Baseband to RFIC.

It supports the following standards: CSI-3, DSI-2, Uniport-M (UniPro1.41) LLI and JC-64.1 UFS.

By using efficient BURST mode operation with scalable speeds, significant power savings can be obtained.

Selection of signal slew rate and amplitude allows reduction of EMI/RFI, while maintaining low bit error rates.

MIPI M-PHY in SMIC 90LL

Overview

Key Features

- Supports MIPI Standard for M-PHY v3.0.

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports HS modes GEAR 1-2

- Supports all Type-I LS modes (GEAR 0-7)

- 1- 3Gbps data rate in HS mode

- 0.01-576Mbps data rate in LS mode

- Suitable for copper and optical media

- Mixel’s LegorithmicTM approach allows for large number of different configurations

- Low power dissipation

Benefits

- Silicon proven in SMIC 90LL

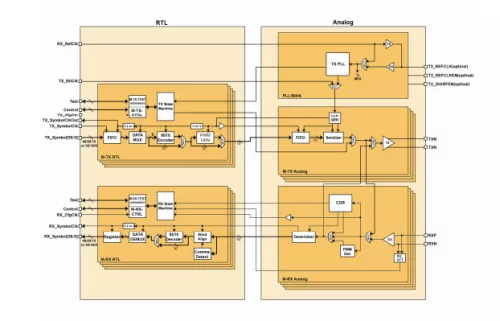

Block Diagram

Applications

- Mobile

- Displays

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

- Storage

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Foundry, Node

SMIC 90nm LL

Maturity

Silicon Proven

Availability

Now

SMIC

Silicon Proven:

90nm

LL