MIPI M-PHY DigRF Compliant IP

Overview

The MXL-M-PHY-DIGRF is a high frequency low-power, low-cost, Physical Layer IP compliant with the MIPI Alliance Standard for M-PHY and DigRF. The IP can be used as a physical layer for the Baseband to RFIC interface. It supports the DigRF v4 standard. By using efficient BURST mode operationwith scalable speeds, significant power savings can be obtained. Selection of signal slew rate and amplitude allows reduction of EMI/RFI, while maintaining low bit error rates. The core employs Mixel’s Legorethmic approach, enabling efficient implementation of multiple configurations.

Key Features

- Complies with MIPI Standard for M-PHY, Draft Specification v0.90.00- r02 and DigRF v4 V1.10.00.0.04

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports HS mode (GEAR 1-2, A & B)

- Supports LS mode (Sys-Burst)

- 1.25-3Gbps data rate in HS mode

- 19.2-52Mbps data rate in LS mode

- Suitable for copper and optical media

- Low power dissipation

- Mixel’s Legorithmic approach efficiently supports large number of different configurations

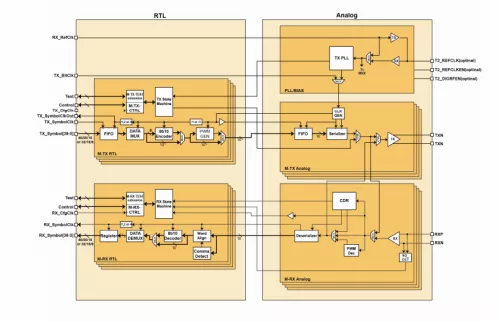

Block Diagram

Applications

- Mobile

- Displays

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

- Storage

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Maturity

Upon Request

Availability

Now

SMIC

Pre-Silicon:

65nm

LL

TSMC

Silicon Proven:

65nm

LP