MIPI D-PHY TRx 8nm

Overview

The MIPI D-PHY IP is a hardmacro PHY for CSI RX or DSI TX. IO pads and EDS structures are included. Extensive built-in self test features such as loopback and scan support. It offers a cost-effective and low-power solution.

Key Features

- Samsung Foundry 5nm low power enhanced (8LPU) CMOS device technology

- 1.8V±5%, 1.2V±5%, 0.75/0.85V±5% power supply

- Fully supports MIPI D-PHY v2.0 HS/LP/ILPS Tx/Rx (Backward Compatible with previous versions)

- Supports 80-400Mbps in D-PHY HS mode

- Global operation timing parameters control

Benefits

- Low power consumption, small area

- Supports both overdive (0.85V) and normal (0.75V) power

- Support for various lane configurations

- Built-in self-test features capable of producing and checking PRBS random pattern

- Highly validated structure in various processes

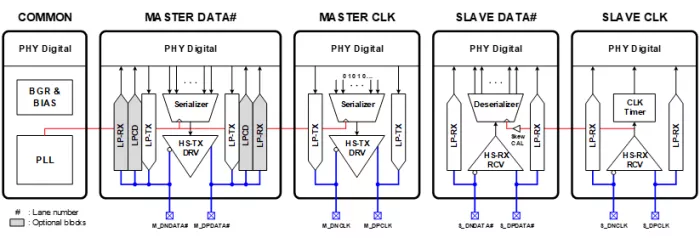

Block Diagram

Applications

- Mobile, Automotive, IoT, DDI, TCON, etc.

Deliverables

- FE-Common: MODEL, TWRAP, TB, LEF, LIBERTY, IPXACT, ATPG, SIPI

- BE-Common: CIR, GDS, DRC, LVS, DFMC

- DOC-Common: Datasheet, User Guide, Test Guide, Register Setting Guide, Supplement Guide, PLL Datasheet, PLL Calculator

Technical Specifications

Short description

MIPI D-PHY TRx 8nm

Vendor

Vendor Name

Foundry, Node

Samsung Foundry 8LPU

Maturity

Silicon Proven

Availability

Now

Samsung

Silicon Proven:

8nm