Low Power Frac-N PLL on GLOBALFOUNDRIES 40LP

A programmable on-the-fly Fractional-N PLL is required to lock to an incoming clock source and produce an output clock.

Overview

A programmable on-the-fly Fractional-N PLL is required to lock to an incoming clock source and produce an output clock. The generated clock needs to be locked to the input source but maintain a high-degree of precision, hence an on-the-fly programmable fractional feedback divider is required (“on the fly” meaning the frequency transition and re-obtaining lock process for small frequency adjustment is glitch free and contains limited frequency over/undershoot).

The Fractional-N PLL macro is implemented in Analog Bits’ proprietary architecture that uses core and IO devices. The PLL resides inside the IO ring that includes two analog power supply pads, occupying no core area. In order to minimize noise coupling and maximize ease of use, the PLL incorporates a proprietary ESD structure, which is proven in several generations of processes. Eliminating band-gaps and integrating all on-chip components such as capacitors and ESD structures, helps the jitter performance significantly and reduces stand-by power. The Fractional-N PLL macro fits into any standard IO pad pitch and can be implemented in staggered and in-line IO configurations.

PLL Operational Range Description Symbol Min Typ Max Units Input Frequency FREF 5 60 MHz Post-Divide Reference frequency FPFD 7 200 MHz VCO Frequency FVCO 2400 MHz Output Frequency FOUT 20 1200 MHz Output Duty Cycle tDO 45 55 % Total area of macro (excluding bond pad area) A 0.024 sq. mm May vary depending on size of IO slots Chip core area requirement CA 0 sq. mm Total Power IDD 3 mA Operational Voltage (Digital) VDIG 0.99 1.1 1.21 V Operational Voltage (Analog) VANA 3.0 3.3 3.6 V Operational Temperature TOP -40C 25 175 C Table 1: PLL Operational Range

Key features

- Electrically Programmable PLL for multiple applications including Automotive Grade 0 at 175C operation

- Ability to generate precise system clocks synchronized to track remote sources

- Very fine precision: near 1 part per billion resolution

- Fully integrated 32-bit datapath (8-bit integer plus 24-bit fractional)

- Implemented with Analog Bits’ proprietary architecture

- Fully integrated inside industry standard or other customized IO ring

- Occupies zero core area

- Low power consumption

- Spread Spectrum tracking capability

- Requires no additional on-chip components or band-gaps, minimizing power consumption

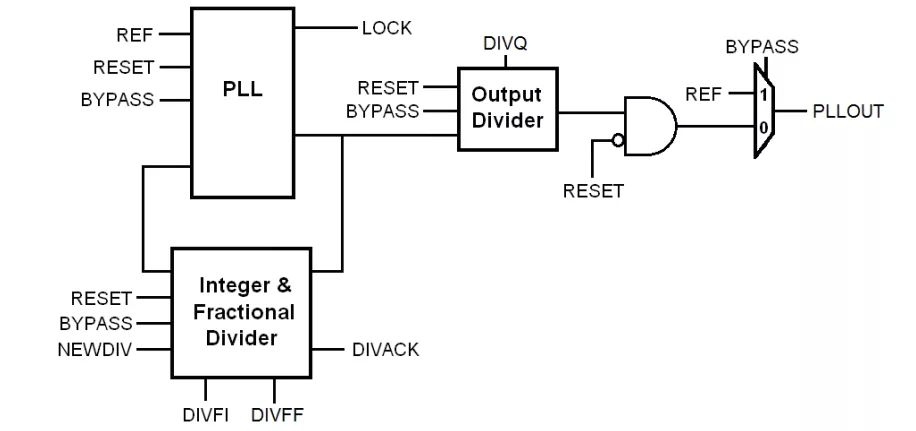

Block Diagram

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 40nm | LP | — |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is Low Power Frac-N PLL on GLOBALFOUNDRIES 40LP?

Low Power Frac-N PLL on GLOBALFOUNDRIES 40LP is a PLL IP core from Analog Bits Inc. listed on Semi IP Hub. It is listed with support for globalfoundries.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.