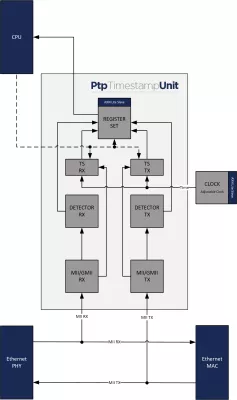

NetTimeLogic’s PTP Timestamp Unit is an implementation of a single port Frame Timestamp Unit (TSU) according to IEEE1588-2008 (PTP). It detects PTP frames on a (R)(G)MII tap and timestamps PTP event frames based on a Counter Clock and provides them delay compensated to a PTP Software stack (e.g. PTPd, PTP4l, etc…). The Timestamp Unit can work as PTP Ordinary Clock (OC) as Master and Slave; it can also be used to build a PTP Boundary Clock (BC) by having multiple instances of the IP core connected to multiple Ethernet ports. All configuration can be written, and timestamps read via an AXI4Light-Slave Register interface.

The IP core comes with a Linux Driver for the Xilinx(R) Zynq 70xx (and as template for integration into other SoCs with AXI interface)

IEEE1588 & IEEE802.1AS PTP Timestamp Unit (TSU) core

Overview

Key Features

- PTP Timestamp Unit according to IEEE1588-2008

- PTP frame detection

- PTP event frame timestamping

- Taps path between MAC and PHY

- Synchronization accuracy: +/- 25ns

- Support for Layer 2 (Ethernet) and Layer 3 (Ip), VLAN, HSR and PRP, Peer to Peer (P2P) and End to End (E2E).

- Master and Slave support

- Full line speed

- AXI4 Light register set

- Configurable Interrupt

- PHY Delay compensation with automatic link speed detection

- MII/GMII/RGMII Interface support (optional AXI4 stream for interconnection to 3rd party cores)

- Linux Driver (MACB & TSU Zynq 70xx)

- Timestamp resolution with 50 MHz system clock: 10ns

Benefits

- PTP Timestamp Unit compatible with PTP4Linux Software Stack

Block Diagram

Applications

- Distributed data acquisition

- Ethernet based automation networks

- Automation

- Robotic

- Automotive

- Test and measurement

Deliverables

- Source Code (not encrypted, not obfuscated)

- Reference Designs

- Testbench with Stimulifiles

- Configuration Tool

- Linux Driver

- Documentation

Technical Specifications

Short description

IEEE1588 & IEEE802.1AS PTP Timestamp Unit (TSU) core

Vendor

Vendor Name

Availability

Now