The I3C Autonomous Target is intended for simple, data acquisition types of applications where a microprocessor is not needed to process the data. Instead, data is exchanged via a simple set of register interfaces to the application and the controller autonomously manages all of the communication to an upstream I3C Controller.

I3C V1.1 Autonomous Target

Overview

Key Features

- Highly configurable core that allows customer to minimize unneeded logic

- Compliant with MIPI I3C V1.1.1

- Compliant with MIPI I3C Basic V1.1.1

- Dynamic addressing

- Single Data Rate (SDR)

- Error detection types (TE0-TE5)

- Advanced I3C features

- Hot join

- In-band interrupts

- Timing Control

- Asynchronous Mode 0

- Synchronous Mode

- High-speed mode (HDR-DDR)

- Group addressing

- Target reset

- All Common Command Codes (CCCs) supported

- Static I2C address support

- Legacy I2C coexistence, including I2C messaging

- Support for I2C pads with 50ns glitch filter

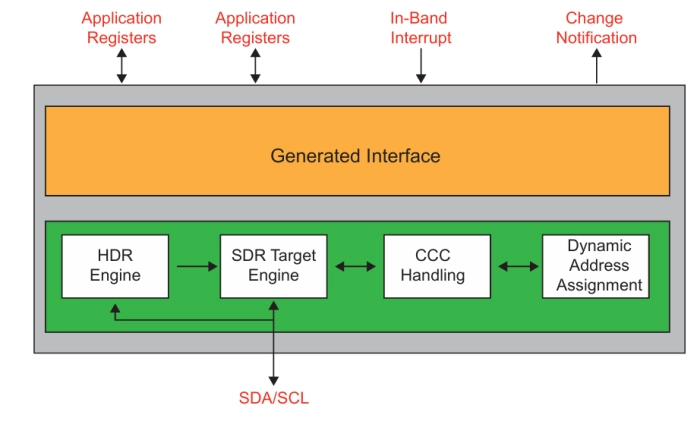

Block Diagram

Applications

- IoT Edge Devices

- Industrial Sensors

- Small Controllers

- Mixed Signal Digital - MEMS

- Smart Sensors

- Smart Lighting

- Temperature, Pressure, Acceleration Monitors

- Personal Health Monitors

- I3C Connected Devices

Deliverables

- Verilog RTL source code

- Test bench with test suites

- Documentation including User's Guide and Integration Guide

- Technology-independent synthesis constraints

Technical Specifications

Short description

I3C V1.1 Autonomous Target

Vendor

Vendor Name

Related IPs

- I3C V1.1 Advanced Target

- MIPI I3C v1.1.1 Basic Controller and Target

- MIPI I3C v1.1.1 Basic Target lite

- MIPI I3C v1.1.1 Controller and Target

- MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification

- MIPI I3C Master v1.1 Controller IP offers impressive data transmission capacity for sensor integration.