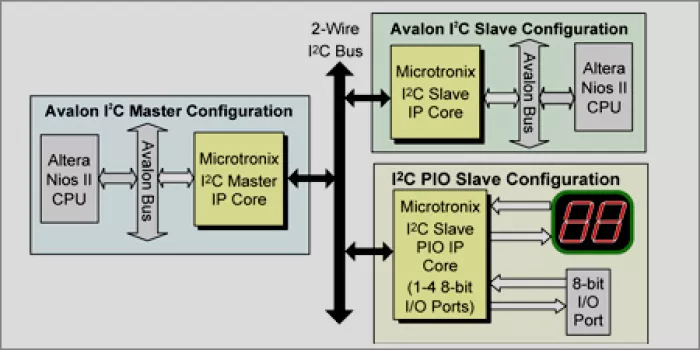

The Microtronix I2C Master/Slave/PIO IP Core is a complete I2C solution offering three modes of operation and support for standard I2C bus transmission speeds. The I2C Master/Slave core provide a generic memory-mapped bus interface. Also designed as an Altera SOPC Builder Ready component, it integrates easily into any SOPC Builder generated system using an Nios® II Avalon bus.

The Microtronix I2C PIO Slave core is provided as an Altera Quartus II Megafunction and integrated into the Altera MegaWizard Plug-in Manager.

The core is optimized for all Altera FPGAs, including the newest generation of Stratix, Arria, Cyclone, and MAX II devices.

Sample applications for uClinux and HAL are provided for components on the I2C bus.

I2C Master-Slave-PIO IP Core

Overview

Key Features

- I2C Master/Slave Transmitter & Receiver IP core

- I2C 8-bit PIO Slave core

- I2C bus transmission speeds; 100Kbps, 400Kbps & 1Mbps

- Own address and general call address detection

- Input clock filter

- Meets Philips I2C -bus specification version 2.1

- 7-bits addressing format

- Single byte transmit and receive buffer

- Santa Cruz I2C development board (optional)

- VHDL

- 300 LE's for Avalon M/S, 100 LE's for PIO

Benefits

- Interfacing your I2C device to the Nios II processor and µClinux has never been easier or more flexible. The µClinux software that comes with the CD includes all source code and a Nios II HAL component with supporting drivers. I2Cdetect, I2Cdump and I2Cset I2C Linux application tools are also included for testing and debugging your I2C application.

Block Diagram

Deliverables

- Encrypted source code

- Altera SOPC Builder component

- HAL Master/Slave drivers & applications

- Linux Master driver

- ModelSim Test Bench

- Includes license and 1 year of updates

- 1-Hour of Installation Support

Technical Specifications

Short description

I2C Master-Slave-PIO IP Core

Vendor

Vendor Name

Availability

Available for immediate sale