Rambus is offering the industry’s first HBM4 Controller IP core designed to support customers with deploying a new generation of HBM memory for cutting-edge AI accelerators, graphics and high-performance computing (HPC) applications.

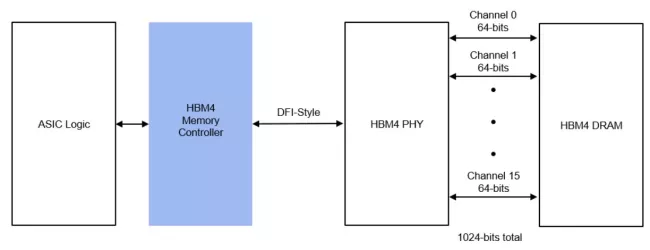

How the HBM4 Controller Works

The core accepts commands using a simple local interface and translates them to the command sequences required by HBM4 devices. It also performs all initialization, refresh and power-down functions. The core queues up multiple commands in the command queue. This enables optimal bandwidth utilization for both short transfers to highly random address locations as well as longer transfers to contiguous address space. The command queue is also used to opportunistically perform look-ahead activates, precharges and auto-precharges, further improving overall throughput. The Reorder functionality is fully integrated into the controller command queue increasing throughput and minimizing gate count.

The controller can be delivered standalone or integrated with the customer’s choice of PCIe 6.2.1 PIPE compliant SerDes.