Overview

The GPIO core is used to create functions in a system that are not implemented with dedicated controllers, and require simple input and/or output software-controlled signals.

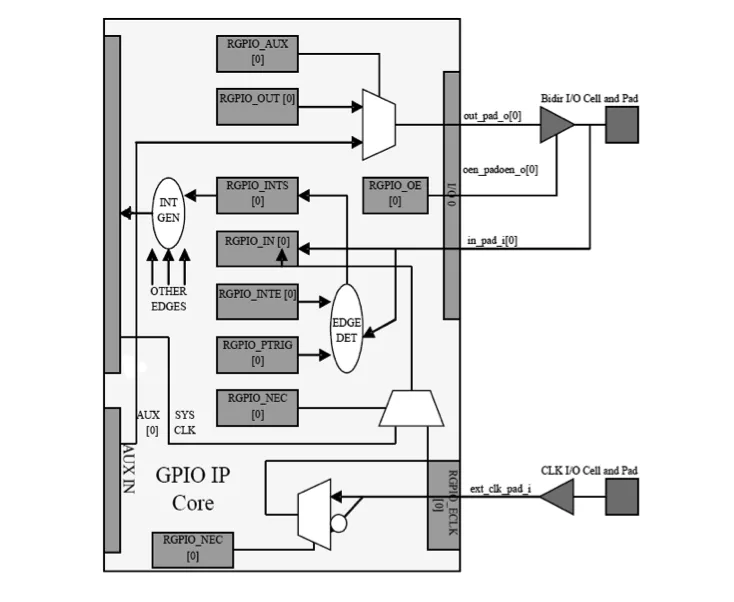

The number of general-purpose I/O signals is user selectable ranging from 1 to 32. For more I/O signals, several GPIO cores can be used in parallel. Each GPIO signal can be programmed individually as an input, an input in interrupt mode, an output, a bi-directional I/O, or as driven by an auxiliary input. GPIO signals programmed as inputs can be registered at the rising edge of the system clock or at a user-programmed edge of the external clock.

The GPIO core is rigorously verified, silicon-proven and available in RTL source or as a targeted FPGA netlist.

Learn more about GPIO IP core

For over a decade, Sofics has collaborated with CERN, the European Organization for Nuclear Research. Sofics has delivered advanced GPIO cells tailored for radiation-hardened applications, supporting CERN’s groundbreaking particle physics experiments.

This paper provides a complete solution to the GPIO Verification for any SoC. GPIO interface is available in every ASIC. To avoid duplicate efforts and (save) time to verify the GPIO interface, we have produced this Generic GPIO verification suite. It is a UVM-based verification environment, with all the necessary subcomponents that are required to verify any GPIO design.

To complete our task as engineers we rely on the tools we use. We collaborated with Siemens EDA solutions back in 2025 on a webinar about how we use their tools to develop our designs and layouts.

Post-quantum cryptography (PQC) is moving from theory to engineering reality. With NIST-standardized algorithms ML-KEM (FIPS 203) and ML-DSA (FIPS 204) now finalized, FPGA developers face a practical challenge: How to integrate these algorithms efficiently on resource-constrained hardware?

The I2C (Inter-Integrated Circuit) Bus invented in 1980 by Philips Semiconductors (NXP Semiconductors today) was a massive step forward in simplifying communications in embedded systems. It is a simple two-wire interface for synchronous, multi-master/multi-slave, single ended serial communication. Fast forward 45 years to today and it is still widely used for attaching low speed peripheral Integrated Circuits (ICs), processors and microcontrollers. But silicon today has changed...