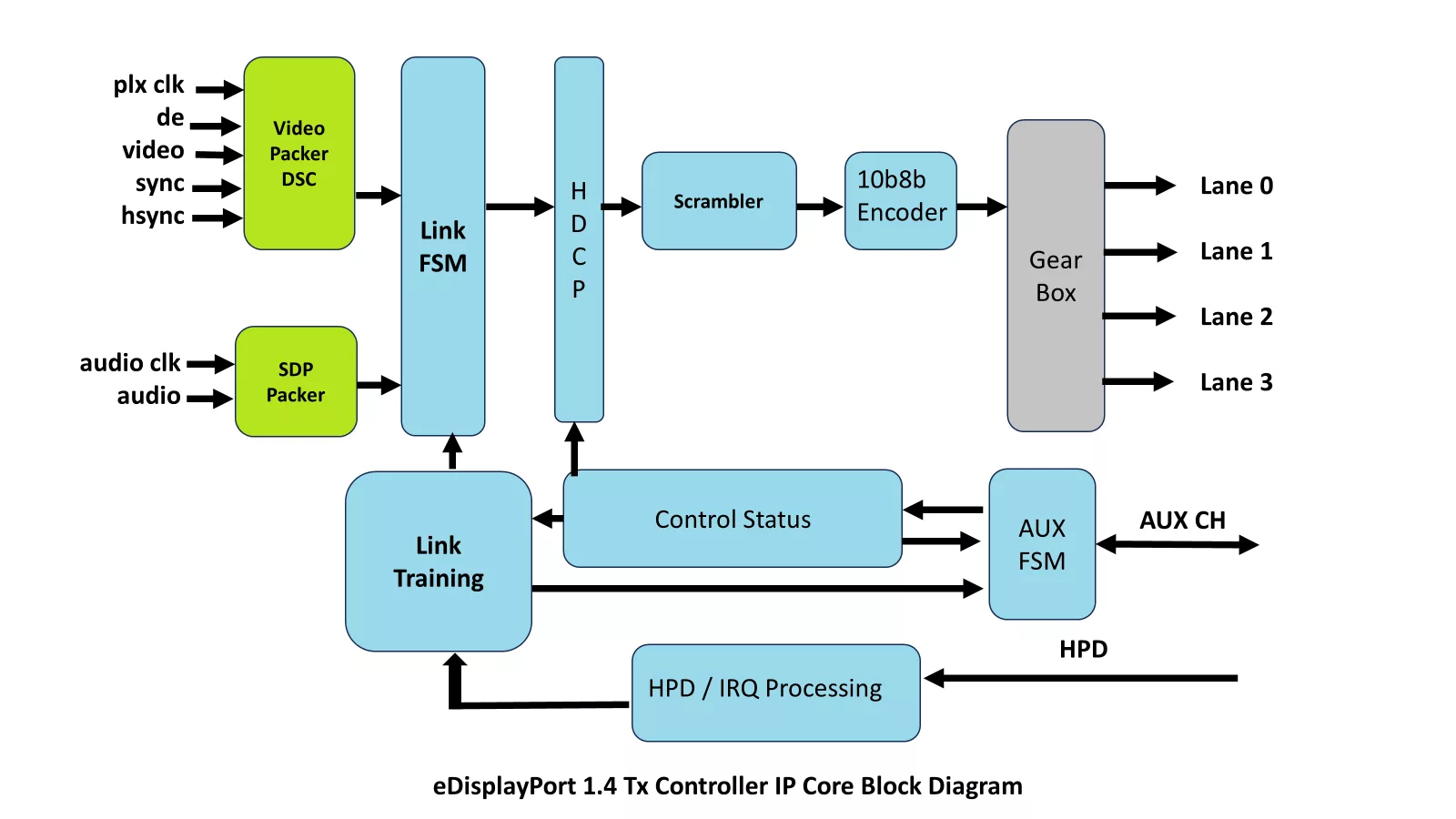

eDisplayPort v1.4 Transmitter Controller IP Core

This eDisplayPort 1.4 Tx Controller IP Core integrates into any SoC or FPGA development, supporting the eDisplayPort 1.4b specifi…

Overview

This eDisplayPort 1.4 Tx Controller IP Core integrates into any SoC or FPGA development, supporting the eDisplayPort 1.4b specification. It can be implemented in any technology and offers compatibility with various host bus interfaces. The IP core is delivered in Verilog RTL and validated using FPGA technology, including RTL code, test scripts, and a test environment. With high bandwidth and resolution support and compatibility for various host bus interfaces, such as AHB, AHBLite, APB, AXI, and more, it enables the transmission of stunning 8K video at 60Hz with deep color and HDR capabilities. The core's flexibility is evident through its compatibility with different lane configurations, allowing designers to choose the setup that suits their system requirements. It optimizes signal integrity through link training, lane alignment, adaptive equalization, and error detection and correction techniques. The IP core also provides exceptional audio support, facilitating synchronized audio and video streaming in popular formats like LPCM, Dolby Digital, and DTS-HD Master Audio. It integrates HDCP functionality to meet content industry requirements, ensuring secure transmission of encrypted content. The eDisplayPort Transmitter IP Core offers configurability, allowing system designers to customize power management, equalization settings, and audio configurations, enabling optimal integration into various system architectures and applications.

Key features

- Supports eDP 1.4b specification

- Supports full eDP Transmitter functionality

- Supports multi lanes upto 4 lanes.

- Supports main link, Aux link and Hot plug functionality

- Supports packing of all the video formats supported by the display port

- Supports HPD based link training.

- Supports interlane skew insertion in source mode

- Supports scrambler as in Display port specification

- Supports scrambler reset after every 512th symbols.

- Supports RGB, YCBCR444, YCBCR422, YCBCR420, Y-Only and RAW color format.

- Supports PSR (Panel Self Refresh) entry and exit.

- Supports frame number identification in PSR.

- Supports Selective update (partial frame update) during Panel Self Refresh (PSR)

- Supports PSR2(Panel Self Refresh) as per spec eDPv1.4b

- Supports Multi SST operation(MSO) • Two SST Links with one Lane each (two Lanes total), 2x1 • Two SST Links with two Lanes each (four Lanes total), 2x2 • Four SST Links with one Lane each (four Lanes total), 4x1 Supports Advanced Link Power Management to reduce wake latency

- Supports GTC-based video timing synchronization

- Supports Display stream compression as per spec eDPv1.4b

- Supports PSR Secondary Data Packet.

- Supports Display Backlight Control Using DPCD Registers. Supports 10bit, 20bit, 40bit, and 80bit parallel interfaces

- Supports high-bandwidth Digital Content Protection System version1.3 (HDCP v1.3)

- Supports high-bandwidth Digital Content Protection System version2.2 (HDCP v2.2) • Supports for HDCP2.2 with full authentication • Supports for HDCP2.2 with bypass the authentication

- Supports high-bandwidth Digital Content Protection System version2.3 (HDCP v2.3)

- Fully synthesizable, Static synchronous design

- Positive edge clocking and no internal tri-states

- Simple interface allows easy connection to microprocessor/microcontroller devices

Block Diagram

Benefits

- Fully compliant, silicon-proven core

- Comes with Verilog testbench and option to buy full advanced System Verilog Testbench

- Support directly from engineer who designed the code

- Based on RMM (Re Use Methodology Manual guidelines)

- Supports all the Synthesis tools

What’s Included?

- RTL design in Verilog.

- Lint, CDC synthesis script with waiver files. Lint, CDC synthesis reports.

- IP-XACT RDL generated address map.

- Firmware code and Linux driver package.

- Technical documentation in greater detail.

- Easy to use Verilog test environment with Verilog test cases.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Displayport IP core

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

DisplayPort 2025: Navigating the Next Wave of Display Innovation

Audio Transport in DisplayPort VIP

DisplayPort 2.1 vs DisplayPort 1.4: A Detailed Comparison of Key Features

Frequently asked questions about DisplayPort IP cores

What is eDisplayPort v1.4 Transmitter Controller IP Core?

eDisplayPort v1.4 Transmitter Controller IP Core is a Displayport IP core from T2M GmbH listed on Semi IP Hub.

How should engineers evaluate this Displayport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Displayport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.