The GRSCRUB is an FPGA configuration supervisor responsible for programming and scrubbing the FPGA configuration memory to prevent accumulation of errors. The GRSCRUB IP is currently able to supervise FPGAs of the Kintex UltraScale and Virtex-5 Xilinx FPGA families. The IP can be set to scrub the entire FPGA configuration memory or just a defined memory area. GRSCRUB is intended to be used as an external entity to the FPGA being supervised.

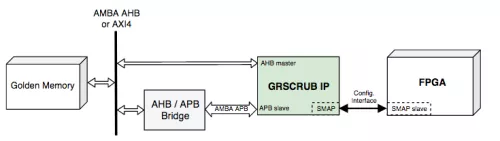

GRSCRUB accesses the FPGA configuration memory through the SelectMap interface. In addition, the GRSCRUB accesses through an AMBA AHB or AXI4 bus a Golden memory that can be ROM or RAM. The original configuration bitstream is stored in the Golden memory, and it is used both to configure the FPGA at start-up and to repair the FPGA configuration memory in case of errors. The Golden memory also stores the mask data and the Cyclic Redundancy Check (CRC) codes used to check the configuration bitstream integrity.

The scrubbing mitigation technique fixes bit-flips in the FPGA configuration memory, leaving up to the user to apply any additional method to mask errors and re-establish the state of the system. Scrubbing does not cover soft-errors affecting User memory data. All dynamic data stored in memory elements, such as shift-registers (SRL), LUT RAMs, and Block RAMs (BRAM), are not verified by GRSCRUB.

FPGA Supervisor

Overview

Key Features

- FPGA configuration

- Mapping FPGA frame addresses

- Blind scrubbing

- Readback scrubbing: Full Frame Check (FFC) and CRC32 error detection

- Detect and correct single and multiple errors

- SelectMap access (external FPGA interface)

Block Diagram

Deliverables

- The GRSCRUB IP core is available in VHDL source code for ASIC and FPGA implementations.

- The GRSCRUB controller will be included in our coming standard products such as the GR716B microcontroller.

Technical Specifications

Related IPs

- High Performance SHA-1 Hash Core for Xilinx FPGA

- High Performance DES and Triple-DES core for Actel FPGA

- 1394b FPGA Link Layer Controller

- Spartan-6 FPGA Integrated Endpoint Block for PCI Express (PCIe)

- Dual SATA Host controller on Virtex 5 FXT FPGA

- ChipScope Pro IBERT for Virtex-6 FPGA GTX Transceivers