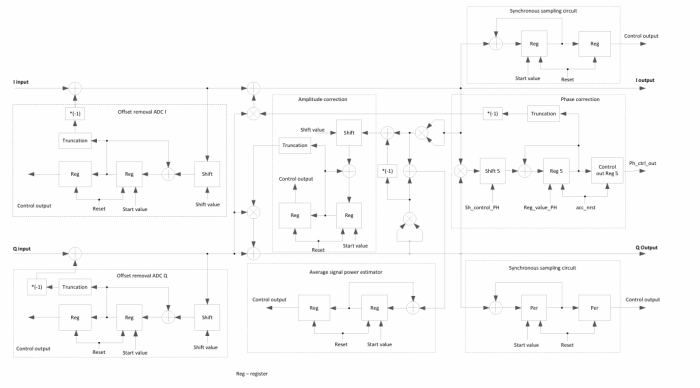

This IP provides a DC offset removal at the ADC output, the channel amplitude and phase imbalances cancelation. The corrector is fully parameterized allows you to quickly control the speed of convergence of the each chain correction. The block diagram contains the average signal power estimator required for the subsequent removal amplitude imbalance of the channels. The synchronous sampling circuits are used to eliminate the phase error between the reception channels for the automatic gain control and diagnostics. The corrector incorporates four feedback loops, each of which is responsible for adjusting individual parameters of the complex signal from the ADC. Upon opening of the loops, the unit operates in the transmission mode to output without change.

Corrector ADC

Overview

Key Features

- SMIC EEPROM CMOS 90 nm

- Control ADC offset

- Control amplitude imbalances

- Control phase imbalance

- Estimates average signal power

- FPGA and ASIC implementations available

- Portable to other technologies (upon request)

Block Diagram

Applications

- DSP systems

- Digital receivers

Deliverables

- xHDL behavior model

- Documentation

Technical Specifications

Short description

Corrector ADC

Vendor

Vendor Name

Foundry, Node

SMIC EEPROM CMOS 90 nm

Maturity

Silicon proven

Availability

Now

SMIC

Silicon Proven:

90nm

LL