Arasan’s CAN-SEC Acceleration Engine Core implements the CAN-XL Protocol (CiA 610-1), CAN-XL Addon Part 1-Simple/Extercontent Indication (CiA 613-1), and CAN-XL Addon Part 2-Security (CiA 613- 2) Protocols.

Arasan’s CAN-SEC Acceleration Engine core is easy to integrate with the Host processor using AMBA-APB, AHB_Lite or AMBA-AXI standard interface. This highly configurable design supports programmable Interrupts, data and baud rates, acceptance filters & buffering schemes specific to the application.

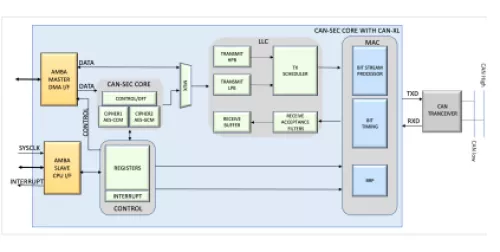

CAN-SEC Acceleration Engine

Overview

Key Features

- ASIL-C, ISO26262 Certified, Automotive Grade

- CAN-SEC Acceleration Engine Supports

- CAN-XL Protocol (CiA 610-1)

- CAN-XL Addon Part-1 (CiA 613-1)

- CAN-XL Addon Part-2 Security (CiA-613-2)

- AES-CMAC for Encryption

- AES-GCM for Authenticated Encryption

- Key Size-128,192 or 256 bits

- Up to 256 CAN-SEC secure channels

- Interfaces

- Simple AMBA-APB, AMBA-AHB-Lite or Generic RAM like interfaces

- Unique Benefits

- Embedded DMA for reducing Gate count by moving Buffers outside the Controller

- Easily configured to support AMBA-AXI4

- Advanced Features

- SDB-Software Defined Buffers, to support large external and small internal memories with minimum latency

- Optimized design for short data frames to create latency advantage

- Highly configurable design for data rate, baud-rate, interrupt sources and mix-bit options

- Low software overhead, future-proof design

- RAS Features

- Advanced Error management unit prevents data loss during transmission and prevents message collisions

- Designed to increase reliability, faster error reporting

- Frame or Format error reporting is done on the receiver side in a timely manner

- Supports debug, system maintenance and system optimization for Last error types, Arbitration lost position, error threshold indicators and others

- Loopback mode for debug and self-testing during integration and system bring-up

Benefits

- Arasan announces the ISO26262 ASIL-C functional certification of its 2nd generation CAN Trio supporting CAN 2.0, CAN FD and CAN XL with CANsec IP for secure CAN Bus transactions.

Block Diagram

Video

ARASAN CAN FD IP SOLUTION FPGA DEMO

Arasan, a leading provider of semiconductor IP for all things mobile, including automobiles released its 2’nd generation of CAN IP FPGA demo video.

Deliverables

- System Verilog RTL Source Code

- A simplified Testbench with simulation models to run initial set of tests after release

- Synthesizable Netlist

- Synthesis Scripts and exception lists

- Timing Report

- Protocol Compliance & Coverage Report

- Sample Firmware with Drivers

- Application Notes

Technical Specifications

Maturity

Silicon proven

Availability

Now