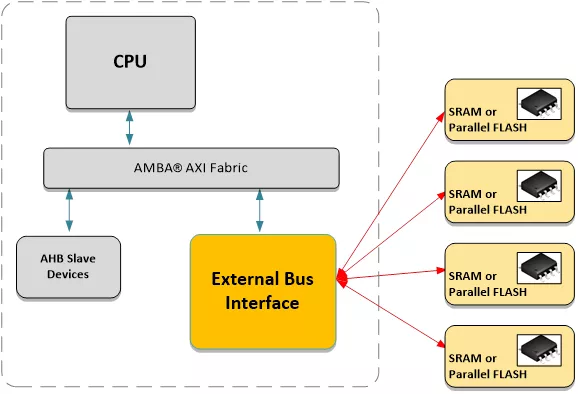

AXI External Memory Controller

Overview

The AXI External Bus Interface (EBI) allows the processor to transmit and receive data to an external device, usually a memory (SRAM, Flash, etc.). The number of read wait states, the number of write wait states, and the memory width are all configurable through the APB register interface of the EBI. The EBI allows word, half-word, and byte width addressing to 64-bit, 32-bit, 16-bit, and 8-bit external devices.

Key Features

- Interfaces AXI bus to external SRAM or Parallel Flash devices

- AMBA® AXI Compatible

- Supports 8-bit, 16-bit, 32-bit and 64-bit external modes

- Supports byte (8-bit), halfword (16-bit), word (32-bit) and dword (64-bit) internal accesses

- Independent programmable wait states per device interface

- Selects up to 4 external devices

Block Diagram

Deliverables

- Verilog Source

- Complete Test Environment

- AXI Bus Functional Model

- C-Sample Code

Technical Specifications

Short description

AXI External Memory Controller

Vendor

Vendor Name

Maturity

Silicon Proven

Availability

Now

Related IPs

- AMBA AHB Direct Memory Acess (DMA) Controller

- NVMe IP core -- Directly connect PCIe SSD without external memory

- AXI4-Stream to/from AXI Memory Map - AXI4-Stream Conversion to AXI Memory Map, 16 Channels

- AXI4-Stream to/from AXI Memory Map - AXI Memory Map Conversion to AXI4-Stream, 16 Channels

- AXI4-Stream to/from AXI Memory Map – 2 DMA Channels - Control by SGL Descriptors

- AXI4-Stream to/from AXI Memory Map – 2 DMA Channels - Control by SGL Commands Streams