Arm Cortex-A53

Overview

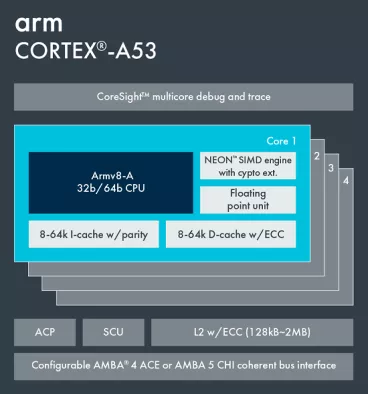

The Cortex-A53 processor has one to four cores, each with an L1 memory system and a single shared L2 cache.

Key Features

- In-order pipeline - Lower power consumption.

- Extensive dual-issue capability - Increased peak instruction throughput via dual instruction decode and execution.

- Advanced branch predictor - Increased branch hit rate with 6Kb Conditional Predictor and 256 entry indirect predictor.

- Extensive power-saving features - Hierarchical clock gating, power domains, advanced retention modes.

Benefits

- High efficiency processor for a wide range of applications in mobile, DTV, automotive, networking, storage, aerospace, and more.

- High value Armv8-A architecture for standalone entry level designs.

- Versatile, can be paired with any Armv8.0 core in a big.LITTLE configuration, including Cortex-A57, Cortex-A72, other Cortex-A53, and Cortex-A35 processors.

- Mature product with high volume shipment.

- This processor can also be implemented in an Arm big.LITTLE configuration.

Block Diagram

Applications

- Premier to mid-range smartphones

- Aerospace

- Networking

- Storage networking (HDD

- SDD)

- Automotive infotainment

Technical Specifications

Short description

Arm Cortex-A53

Vendor

Vendor Name