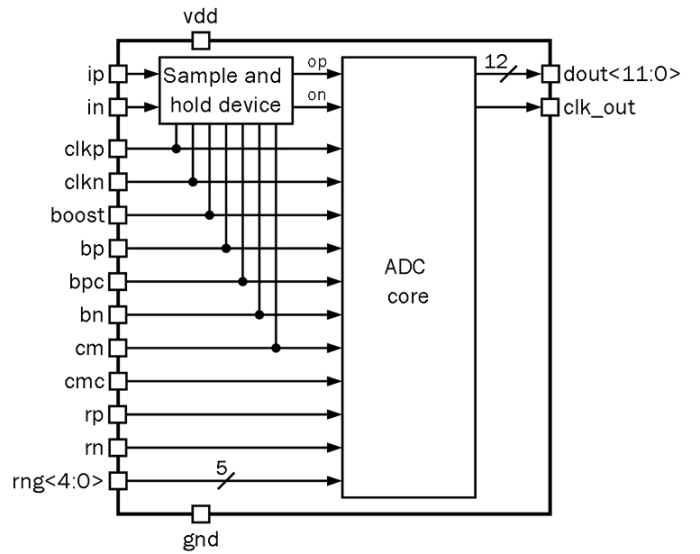

250iHP_ADC_03 is a low-power high-speed 12-bit ADC that employs high-performance differential pipeline architecture. The block consists of a sample and hold device, a core ADC and block of comparators. The ADC requires: 2.5 V analog supply, differential reference voltages 1.5 V and 1.0 V, common mode voltage 1.25 V and differential input clock. The ADC supports standby mode which allows state with minimum power consumption. There is also the ability to configure the operating modes of the ADC by using digital registers.

12-bit 1-channel 15 to 25 MSPS pipeline ADC

Overview

Key Features

- iHP SGB25V

- Resolution 12 bit

- Sampling frequency 15 to 25 MHz

- Low power consumption in standby mode

- High values of signal/noise ratio (60 dB)

- Spurious-free dynamic range 62 dB

- Portable to other technologies (upon request)

Block Diagram

Applications

- Optical networking

- Test equipment

- Portable ultrasound and digital beam-forming systems

- Telecommunication systems

- Higher quality imaging in video systems

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

12-bit 1-channel 15 to 25 MSPS pipeline ADC

Vendor

Vendor Name

Foundry, Node

iHP SiGe BiCMOS 0.25µm

Maturity

Silicon proven

Availability

Now