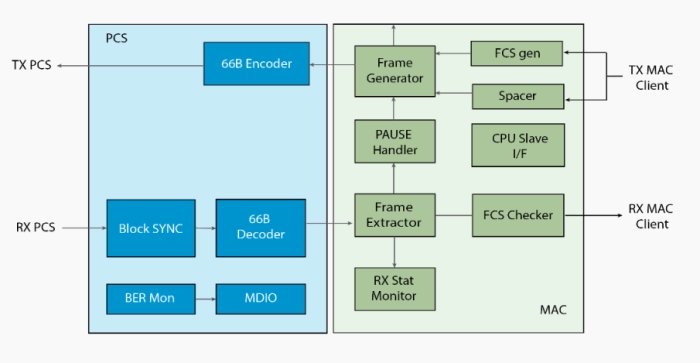

OmegaCORE 10G/25G MAC/PCS/FEC is the fully integrated Physical Coding Sublayer (PCS), KR4 FEC and Media Access Controller (MAC) core for 10G/25Gbps Ethernet applications which is complaint with IEEE 802.3by standard. The interface to the PMA supports a single 10G/25Gbps bi-directional, serial interface. The PCS sublayer includes 66B encoding, transcoding and scrambling. This Core also supports CPRI-8, 9 and 10 PCS mode configurable through software register.

The north-bound interface from the MAC provides a configurable 64-bit system interface.

The southbound interface performs the mapping of transmit and receive data streams (at the PMA layer) to the on-chip SERDES.