How to cost-efficiently add Ethernet switching to industrial devices

By Comcores

Introduction

Ethernet is widely preferred for connectivity in modern manufacturing sites, as well as in in-vehicle automotive and avionics networks. Ethernet’s advantages over legacy technologies include faster speeds, lower costs, scalability, and the ability to handle various types of data traffic on a single network. The growing demand for Ethernet connectivity prompts device manufacturers to integrate Ethernet functionality into their devices. However, selecting the right features for each device type can be challenging. Additionally, Ethernet may not be the primary technology focus of a device company. This blog explores critical considerations and solutions for implementing Ethernet switches tailored to industrial applications, emphasizing required features and cost-effectiveness.

Industrial Ethernet

Industrial Ethernet refers to the use of standard Ethernet protocols in an industrial environment. It involves applying Ethernet technology to connect Controllers (PLCs), I/O devices (sensors and actuators), Drives, Human-Machine Interfaces (HMIs), and Industrial networking devices in manufacturing plants. Ethernet offers several advantages over traditional Fieldbus and CAN technologies, such as high-speed communication, scalability, and interoperability with existing enterprise networks and the internet. It enables the integration of various industrial devices into a single network, allowing for centralized monitoring, control, and automation of industrial processes.

Typical network topologies include star, ring, and bus configurations. In a star topology, each device connects to a central multi-port switch, ensuring simple management and robust fault isolation. This topology is often used in control rooms and central processing areas. The ring topology connects several switches, offering redundancy and allowing network recovery if a single link between two switches fails. It is commonly employed in production lines and critical infrastructure areas where continuous operation is essential. The bus topology connects devices along a single line through daisy-chaining 2-port switches within the devices. This cost-effective configuration is typically used for connecting sensors and monitoring systems.

To meet the specific demands of industrial networks, several new features have been added or adopted into the IEEE 802.1 and 802.3 Ethernet standards. Single Pair Ethernet (SPE) is defined as 10/100/1000BASE-T1 interfaces, and PHYs supporting those interfaces are available from several vendors. SPE is designed to run over a single twisted pair of copper wires, as opposed to the traditional 2-4 twisted pairs used in standard Ethernet. This compatibility makes it easier to integrate Ethernet into existing industrial infrastructures. While RJ45 connectors are commonly used for standard Ethernet, SPE often uses different connectors optimized for single pair cabling, ensuring robust and reliable connections suitable for industrial environments.

For data traffic requiring precise synchronization, IEEE 802.1AS can be used to distribute a common clock to multiple devices. Furthermore, Time-Sensitive Networking (TSN), a set of standards related to the IEEE 802.1Q VLAN and priority classification, enables deterministic transmission of packets. It achieves this by assigning certain time slots for certain classes of service, thereby reserving bandwidth for high-priority traffic. At the same time, lower priority traffic (best effort) can use the remaining bandwidth. This allows both deterministic, high-priority traffic and non-deterministic, best-effort traffic to coexist in the same network, which is one of the major benefits of TSN-enabled Ethernet.

Use cases

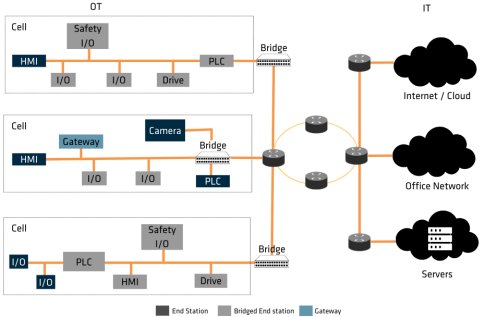

Figure 1: Schematic overview of Industrial Ethernet with routers, bridges, bridged end stations, end stations and gateways.

In general, industrial networks can contain the following different types of Ethernet-enabled devices:

- Routers – multiport devices forwarding based on L3-L4

- Bridges – multiport devices forwarding based on L2

- Bridged End Stations – few port devices forwarding based on L2

- End Stations – terminating Ethernet

- Gateways – terminating Ethernet and connecting to non-Ethernet enabled devices

End stations can include controllers, I/O devices (sensors and actuators), drives, and Human-Machine Interfaces (HMI). Bridged End Stations enable devices to be daisy-chained together and therefore typically require two Ethernet ports. Some devices, such as safety buttons, require deterministic, low-latency connectivity, while others like cameras and monitors might require best effort only.

The most common Ethernet speeds used in industrial environments range from 10/100 Mbps (Fast Ethernet) to 1 Gbps (Gigabit Ethernet). These speeds are sufficient for most industrial automation applications, providing adequate bandwidth for real-time control, data exchange, and monitoring tasks.

Switch requirements

When defining the requirements for an Ethernet switch for a device there are several factors to consider.

Ports and speeds

The number of ports and the port speeds of the switch are key features. A bridge might require 4 – 16 ports and support up to 1000Mbit/s pr port while a Bridged End Station might need only two ports with 10/100 Mbit/s. The number of ports and speeds also determine the switch core size.

Managed or Un-managed

A managed switch enables the user to configure certain features of the switch whereas an un-managed switch is pre-configured from the vendor. The main benefits of an un-managed switch are lower cost and simplicity of operation. On the other hand, an un-managed switch cannot support features like TSN, VLANs or QoS. Managed switches require a CPU interface in addition to the Ethernet ports.

Cut-through or store-and-forward

Cut-through and store-and-forward are two different methods a switch can use to handle and forward data packets. A cut-through switch starts forwarding a packet as soon as it reads the destination address, which means the switch begins transmitting the packet before it has been entirely received. Cut-through switching generally provides the lowest possible latency but can lead to errors because the integrity of the packets is not checked before transmission. As the name implies, a store-and-forward switch reads and stores the entire packet before starting to transmit it. The main benefit of this approach is that the integrity of the packet can be checked before transmission, allowing erroneous packets to be discarded. The drawback is that store-and-forward switching generally leads to longer latencies.

TSN and synchronization

TSN offers deterministic packet delivery with guaranteed minimum latency, making it essential for handling mission-critical data such as a safety button activation. Supporting TSN requires the switch to be managed, support 802.1AS synchronization and 802.1Q VLAN and priority including 802.1Qbv. For non-mission-critical devices, supporting IEEE802.1AS synchronization may still be relevant if device functions need network synchronization, while devices like surveillance cameras may not require TSN or synchronization.

Security

For devices handling sensitive data that requires confidentiality and security, MACsec (Media Access Control Security) can be utilized. MACsec is a security standard providing encryption and integrity verification for Ethernet frames at the Media Access Control (MAC) layer.

Cost

An important consideration for the switch is naturally the cost. Simple field devices like basic sensors (e.g., temperature, pressure) and actuators (e.g., valves, motors) can range from tens to a few hundred dollars, depending on the complexity and application-specific features. More advanced sensors and controllers can range from a few hundred to several thousand dollars. So, it is critical to keep the total cost of the switch relatively low compared to the device cost.

Cost drivers in Ethernet switch implementation

An Ethernet switch can be implemented in three main ways:

- Custom-developed ASIC

- Off-the-shelf ASIC

- FPGA

FPGA versus ASIC

The development process of an Application-Specific Integrated Circuit (ASIC) is typically lengthy and expensive. Additionally, once the ASIC is fabricated, any design changes require a new iteration of the device. Therefore, this approach is most suitable for well-defined, general-purpose devices with high volume potential. On the other hand, the development of a custom ASIC often leads to the lowest per unit cost provided the potential volume of the product is sufficiently high.

Several vendors offer off-the-shelf Ethernet switch ASICs with fixed feature sets. To justify the investment in ASIC development, these devices are generally designed to cover a broad range of use cases. For a specific use case, this often means paying for more features—such as additional ports or speed options—than needed.

In contrast to custom ASICs, a Field-Programmable Gate Array (FPGA) is a type of integrated circuit that can be programmed or reconfigured by the user after manufacturing. This reconfigurability makes FPGAs useful for prototyping, custom hardware applications, and scenarios where requirements may change over time. Furthermore, an FPGA often enables the integration of device specific pre-processing features with the switching functions.

For most industrial devices, an FPGA is often the preferred option over developing a new ASIC because the FPGA solution offers lower up-front investment, faster time to market, flexibility, and lower risk, especially for low to medium volume applications. It is however important to emphasize that if the volume demand is very high, a custom designed ASIC will be the lowest cost option.

See Table 1 for an overview of the various options.

Table 1: Characteristics of custom developed ASIC, off-the-shelf ASIC and FPGA-based solutions.

Cost drivers of FPGAs and ASICs

The price of an FPGA ranges from a few dollars to thousands of dollars, depending on several factors. A key factor affecting the cost is the “size” of the FPGA, which is measured by the number of Configurable Logic Blocks (CLBs), the number of logic cells, the number of Input/Output (I/O) connections, and the amount of internal memory (RAM). To achieve a cost-effective solution, it is essential to minimize the utilization of the aforementioned resources in the Ethernet switch design, allowing the design to fit into as small an FPGA as possible.

The per-unit cost of an ASIC is primarily influenced by the complexity of its design and the size of its die. Using the latest technology node allows for a smaller ASIC die size. However, development costs rise significantly with more advanced technology nodes. Therefore, custom-designed ASICs often use a technology node a few steps behind the latest one to balance initial investment and per-unit cost. Moreover, reducing the die size can be achieved by optimizing the switch implementation to minimize the use of gates.

Whether the target silicon for the switch is an ASIC or an FPGA, a compact design of the switch will help to drive down the per unit cost.

Compact switch implementation

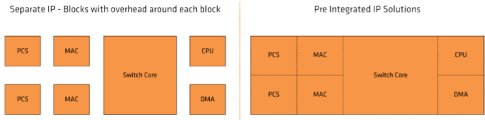

An Ethernet switch typically comprises various distinct functions, including the Physical Coding Sublayer (PCS), Media Access Control (MAC), Switch core, Direct Memory Access (DMA), and CPU Interface. A common approach involves combining individual IP blocks of each function into a full system, as schematically illustrated on the left side of Figure 2. As depicted in the figure, this approach necessitates an overhead around each IP block to enable the various blocks to interface with each other in a standardized manner.

Figure 2:Schematic illustration of Ethernet switch size. Left: traditional approach combining stand-alone IP-blocks (orange areas) with overhead (light blue areas). Right: Pre-integrated solution implementing the switch as one IP-block.

As discussed in the preceding section, the focus in cost-efficient switch design should be on minimizing the utilization of internal chip resources. The traditional method of combining individual IP blocks results in significant overhead in size and complexity due to interface layers needed to connect the IP blocks in a standardized manner.

Integrating all IP blocks into a single IP block solution, as illustrated on the right in Figure 2, reduces overhead significantly. This approach enables more efficient utilization of chip resources, thereby reducing the overall solution’s size. Consequently, this pre-integrated solution facilitates the use of the smallest and hence lowest-cost FPGA or ASIC available.

An important benefit of the pre-integrated switch IP-block solution is that it significantly lowers the risk and complexity of the development process. Combining individual IP-blocks can lead to challenges with timing and increased power consumption, whereas a fully pre-integrated and tested switch IP-block guarantees performance reliability and seamless operation. Furthermore, a pre-integrated solution minimizes the complexity associated with combining multiple individual IP blocks, thereby reducing the risk of errors.

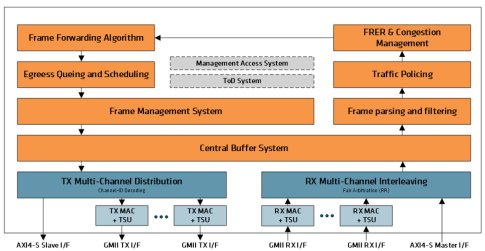

Compact switch solutions from Comcores

The 1G Managed Ethernet TSN Switching IP core from Comcores is the ideal solution for a compact, cost-efficient Ethernet switch targeting industrial, automotive and avionic applications. The switch provides cut-through switching and supports the TSN family of standards. It is compliant to several industrial TSN profiles like 60802: Industrial Automation, P802.1DP: Aerospace onboard Ethernet Communications and P802.1DG: Automotive In-Vehicle Communications, while offering the lowest gate count on the market.

The non-blocking switch enables fine-grained traffic differentiation for rich implementations of packet prioritization enabling per port and per queue shaping on egress ports. The switch supports MAC learning, VLAN 802.1Q, multicast and broadcast as well synchronization according to 802.1AS. Each port supports all the common MII interfaces like GMII, RGMII, and SGMII for attaching Ethernet PHY devices.

While the IP can be customized to your specific requirements, the high-level features of the device are:

- 2 – 63 x 10/100/1000 Ethernet ports

- 25 G cut-through TSN switch core with low latency

- 1 x CPU interface

- Automatic MAC address learning and aging

- IEEE 802.1Q VLAN and QoS support

- TSN features:

-

- IEEE 802.1Q Strict priority scheduling

- IEEE 802.3br Interspersing Express Traffic

- IEEE 802.1Qbu Frame pre-emption

- IEEE 802.1Qbv Time-aware shaping (TAS)

- IEEE 802.1Qav Credit-based shaping (CBS)

- IEEE 802.1AS Timing and Synchronization for Time-Sensitive Applications

- IEEE 802.1Qci Frame Per-stream filtering and policing

- IEEE 802.1Qat Stream Reservation Protocol (SRP)

- IEEE 802.1Qcr Asynchronous Traffic Shaping (ATS)

- IEEE 802.1CB Frame Replication and Elimination for Reliability (FRER)

- IEEE 802.1Qch Cyclic Queing and Forwarding (CQF)

- IEEE 802.1Qdv Enhancement to CQF (also known as Peristaltic Shaper)

- IEEE 802.1AB Link Layer Discovery Protocol (LLDP)

- IEEE 802.1s Multiple Spanning Trees

-

- Extensive statistic reporting

- Optional MACsec support

How to integrate the switch IP

Like all IPs from Comcores the 1G Ethernet switch is available for both ASIC and FPGA, and can be delivered in Source code or Encrypted format. The delivery includes comprehensive documentation, a simulation environment, the programming register specification and timing constraints in Synopsis SDC format.

To help the development of device software, Comcores can also supply software stacks like the 801.2AS software stack.

An FPGA evaluation hardware platform is available for development and testing if the switch is implemented in an FPGA. If the switch is being developed as an ASIC, the FPGA evaluation board can be used for pre-silicon testing and verification. This can significantly reduce the risk of errors in the final silicon.

Summary

In conclusion, Ethernet has emerged as the preferred connectivity solution across diverse industrial applications. Its benefits over legacy technologies include higher speeds, lower costs, scalability, and the capability to support multiple types of data traffic on a unified network. As demand for Ethernet-enabled devices grows, manufacturers face the challenge of selecting appropriate features tailored to each application’s requirements. This blog has explored key considerations and solutions for implementing Ethernet switches in industrial settings, emphasizing the features and cost-effectiveness to meet stringent industrial demands.

Comcores has leveraged extensive experience in integrated circuit design to develop an ultra-compact pre-integrated 1G Ethernet TSN switch IP-block ideally suited for industrial Ethernet. This compact IP allows device manufacturers to add Ethernet switching to their devices cost-effectively. Additionally, the pre-integrated single IP-block eliminates challenges associated with combining multiple separate IP-blocks hereby reducing risk and shortening the time-to-market. Comcores offers customization of the switch IP to precisely match the needs of each device.

Related Semiconductor IP

- NPU IP Core for Edge

- NPU IP Core for Mobile

- NPU IP Core for Data Center

- NPU IP Core for Automotive

- Wi-Fi 7(be) RF Transceiver IP in TSMC 22nm

Related White Papers

- New Ethernet Adaptation Layer Adds Control Option to MIPI A-PHY Automotive Networks

- Growing demand for high-speed data in consumer devices gives rise to new generation of low-end FPGAs

- Technologist backs low-voltage CMOS for SoC devices

- Mobile Devices: RISC-Java blend powers cores

Latest White Papers

- Customizing a Large Language Model for VHDL Design of High-Performance Microprocessors

- CFET Beyond 3 nm: SRAM Reliability under Design-Time and Run-Time Variability

- Boosting RISC-V SoC performance for AI and ML applications

- e-GPU: An Open-Source and Configurable RISC-V Graphic Processing Unit for TinyAI Applications

- How to design secure SoCs, Part II: Key Management