Other

All offers in

Other

Filter

Compare

14

Other

from

8

vendors

(1

-

10)

-

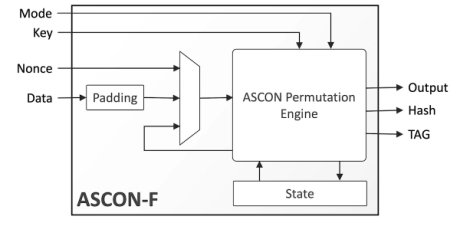

ASCON Authenticated Encryption & Hashing Engine

- The ASCON-F IP core is a compact, high-throughput hardware engine implementing the lightweight authenticated encryption with associated data (AEAD) and hashing algorithms described in the Ascon v1.2 specification.

- A single instance of the ASCON-F IP core can encrypt or decrypt data using the Ascon-128 and Ascon-128a functions or perform Cryptographic hashing Hash per the Ascon-Hash and Ascon-Hasha functions.

-

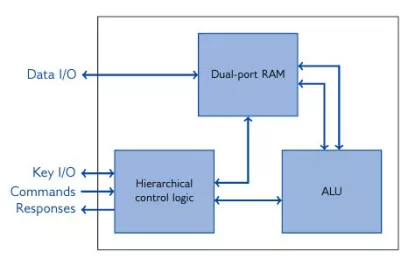

Public Key Accelerator

- Modular exponentiation operations with up to 4096-bit modulus

- Prime field ECC operations with up to 571-bit modulus

- Fastest implementation is 58 kGE and 68 Op/s for 2048-bit RSA, 431 Op/s for 1024-bit RSA, 150 Op/s for 384-bit scalar multiplication

- Smallest implementation is 33 kGE and 67 Op/s for 1024-bit RSA, 24 Op/s for 384-bit scalar multiplication

-

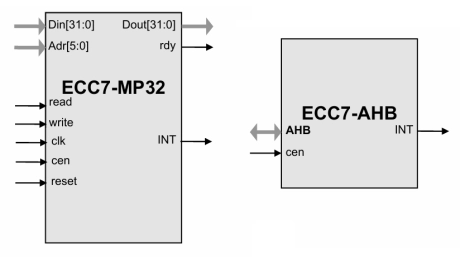

ECC7 Elliptic Curve Processor for Prime NIST Curves

- Elliptic Curve Cryptography (ECC) is a public-key cryptographic technology that uses the mathematics of so called “elliptic curves” and it is a part of the “Suite B” of cryptographic algorithms approved by the NSA.

- The design is fully synchronous, with the exception of the seed part, and available in both source and netlist form.

- The core is supplied as portable Verilog (VHDL version available) thus allowing customers to carry out an internal code review to ensure its security.

-

Curve25519 Key Exchange and Digital Signature IP Core

- Minimal Resource Requirements: The entire XIP4003C requires less than 800 ALMs (Cyclone® 5) and uses only 1-2 multipliers/DSP Blocks2 and 1-2 internal memory block in a typical FPGA implementation.

- Constant Latency: The execution time of XIP4003C is independent of the key value, and consequently provides protection against timing-based side-channel attacks.

- Performance: Despite its small size, XIP4003C can support more than 100 key exchange or digital signature operations per second.

- Standard Compliance: XIP4003C is compliant with RFC7748, RFC8032, and the draft version of FIPS 186-5. XIP4003C can be used as a part of many public-key protocols including IKEv2 (RFC 8031) and TLS 1.3 (RFC 8446).

-

Curve25519 Key Exchange IP Core

- Minimal Resource Requirements: The entire XIP4001C requires less than 1k Logic Elements and uses only 1-2 multipliers/DSP Blocks2 and one internal memory block in a typical FPGA implementation.

- Constant Latency: The execution time of XIP4001C is independent of the key value, and consequently provides protection against timing-based side-channel attacks.

- Performance: Despite its small size, XIP4001C can support more than 100 key exchange operations per second.

- Standard Compliance: XIP4001C is compliant with RFC7748, and can be used as a part of many public-key protocols including IKEv2 (RFC 8031) and TLS 1.3 (RFC 8446).

-

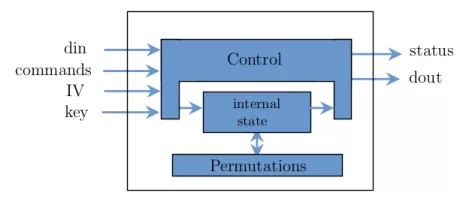

Ascon, A Lightweight Cryptographic Suite for AEAD and Hashing

- Small Resource Requirements

- Versatile Algorithm Support

- Secure Architecture

-

ECDSA (Elliptic Curve Digital Signature) IP Core

- Full ECDSA implementation adhering to Standards for Efficient Cryptography (SEC)

- Bitcoin algorithm support

- Technology-independent HDL model

- Simple external interface for easy adaptation

-

Public-Key Cryptography PKCS IP Core

- Comprehensive implementation in accordance with RSA Laboratories' Public-Key Cryptography Standards (PKCS) series, PKCS #5 v2.0

- Support for SHA256 algorithm

- Technology-independent HDL model

- Simple external interface for easy adaptation

-

Elliptic Curve Digital Signature generation and verification

- Supports any EC over GF(p) of the simplified Weierstrass form that is commonly defined in ECC standards such as NIST, SEC2, Brainpool

-

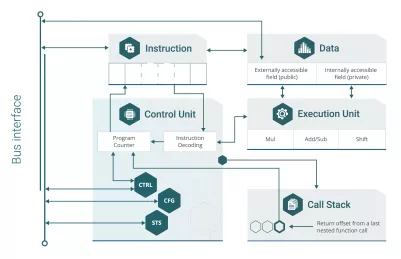

32-bit Public Key Accelerator

- Offloads the computationally intensive parts of public key cryptography

- Support for ARM® AMBA® AHB™/AXI™ and synchronous RAM interfaces

- Integer operations (512-, 768-, 1024-, 1536-, 2048-, 3072-, and 4096-bit)

- ECC-GF(p) operations (160, 192, 224, 256, 384, 512 and 521-bit)