ultra-low power memory IP

Filter

Compare

70

IP

from

26

vendors

(1

-

10)

-

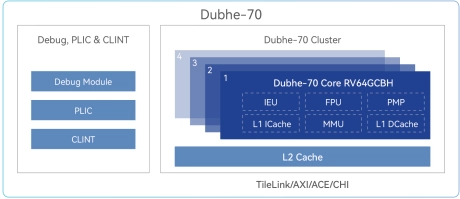

Ultra-low power consumption out-of-order commercial-grade 64-bit RISC-V CPU IP

- Dubhe-70 is a 9+ stage, 3-issue, out-of-order CPU IP that supports the rich RISC-V instruction set, RV64GCBH_Zicond_Zicbom_Zicboz_Zicbop.

- With a score of 7.2 SPECInt2006/GHz, Dubhe-70 targets applications that require highly energy-efficient computation, including mobile, desktop, AI, and automotive.

-

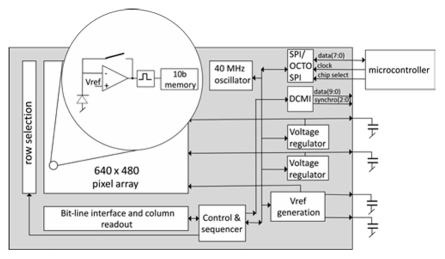

Ultra-low power high dynamic range image sensor

- Resolution: VGA (640 x 480)

- Backside illuminated sensor

- Pixel size: 6.3 μm x 6.3 μm

- Fill factor: 83 %

- Dynamic range: 120 dB intra-scene

-

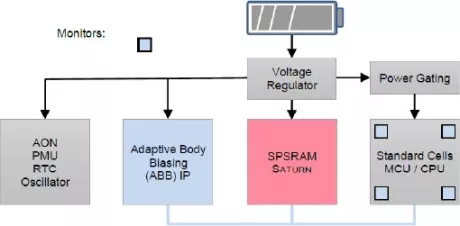

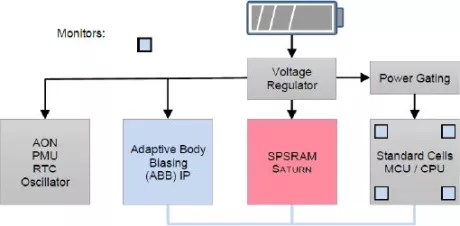

Low Power Memory Compiler - 1-Port Register File Compiler - GF 22nm FDX

- Specifically designed for ultra-low power applications, this memory leverages body biasing to dramatically reduce power consumption.

- Compatible with industry Adaptive Body Biasing IP for PVT and aging compensation

- Body Biasing functionality (up to +1.3V / -1.5V) to reduce leakage or increase speed at the same power

-

Low Power Memory Compiler - Single Port SRAM - GF 22nm FDX

- Silicon proven Single Port SRAM compiler for GF22 FDX - Memory optimized for low power and supports body biasing.

-

ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- 32-bit RISC-V embedded CPU with balanced 3-stage pipeline

- DSP implementation to extend the RISC-V baseline (RMX-100D)

- 2 KB to 64 KB instruction L1 cache

- Up to 2MB instruction and data closely coupled memory (CCM)

-

ARC NPX Neural Processing Unit (NPU) IP supports the latest, most complex neural network models and addresses demands for real-time compute with ultra-low power consumption for AI applications

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

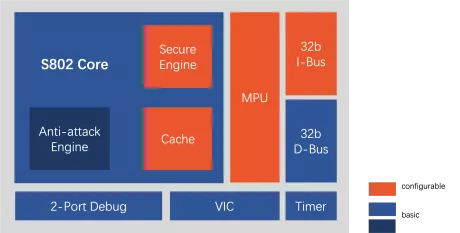

Performance-efficient, ultra-low power, compact ARC SEM security processors help protect against logical, hardware, physical and side-channel attacks

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- RISC, and RISC + DSP 32-bit processors for ultra-low power embedded apps

- Based on the RISC-V ISA, leveraging standard 32-bit protocols (and extensions)

-

Ultra-low power 32-bit processor resistant to physical damage

- Instruction set: T-Head ISA (32-bit/16-bit variable-length instruction set);

- Pipeline: 2-stage;

- General register: 16 32-bit GPRs;

- Bus interface: Dual bus (instruction bus + data bus);

-

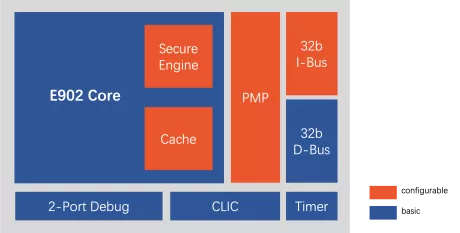

Ultra-low power processor with RISC-V architecture possessing secure execution capability

- Instruction set: T-Head ISA (compatible with RV32EMC/RV32EC/RV32IMC);

- Pipeline: 2-stage;

- Permission mode: Optional M state or M+U state;

- General register: 16 32-bit GPRs;