parallel FFT IP

Filter

Compare

7

IP

from

6

vendors

(1

-

7)

-

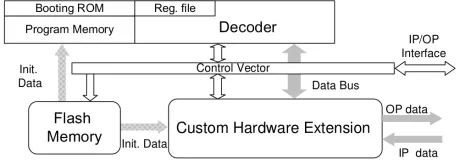

ASIP-1 FFT Engine

- Platform to design Application Specific Instruction Set Processors (ASIPs).

- Ideal for supporting multi-standard systems.

- Supports a wide range of complex DSP functions.

-

Floating Point FFT/IFFT IP Core

- Worlds fastest and most flexible Floating Point FFT IP Core

- Ultra high performance (> 1GSPS possible)

- Custom precision, any exponent and mantissa width

- Clock speeds over 200 MHz in Virtex II Pro

-

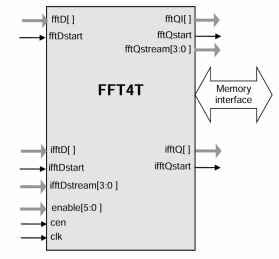

128-Point FFT/IFFT IP Core

- The FFT4T core implements a 128 point complex FFT and IFFT over 12 data streams in hardware. It runs at the clock frequency four times higher than the insput sampling frequency.

- FFT4T core is a specialized FFT/IFFT processor intended for a situation where an RF signal is recieved over multiple channels in parallel and its filtering is to be performed in the frequency domain. The core fits nicely into, for example, a multichannel GPS system.

-

Ultra High Speed FFT/IFFT processor

- Highly pre-synthesis design configurability with detailed generic/parameter values, in order to meet desired implementation trade-offs.

-

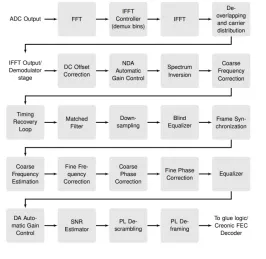

DVB-T2 Demodulator and LDPC/ BCH Decoder

- DVB-T2 EN302 755 V1.2.1, Rev.9 compliant

- Supports IF input

- Single input – Single output (SISO)

- Sampling frequency offset (SFO) tracking and compensation

- Carrier frequency offset (CFO) detection and correction

-

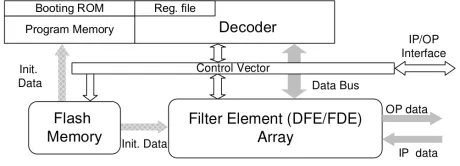

ASIP-2 Programmable Filter Engine

- Platform to design Application Specific Instruction Set Processors (ASIPs).

- Ideal for supporting multi-standard systems.

- Supports a wide range of complex DSP functions

- The ASIP2 performs Fast Fourier Transform (FFT) to convert time domain signals to frequency domain signals for further processing. It supports FFT sizes from 4 to 8K.

-

DVB-S2X Multi-Carrier Demodulator

- Supports CCM, ACM and VCM

- Supports roll-off factors 5%, 10%, 15%, 20%, 25% to 35%

- Support for short and normal blocks (16,200 bits and 64,800 bits) with pilots only

- Support for QPSK to 256-APSK