eDP 1.5 IP

Filter

Compare

6

IP

from

4

vendors

(1

-

6)

-

eDP 1.5 Verification IP

- Fully compliant with VESA Embedded DisplayPort (eDP) Standard 1.5 Specification

- Supports power saving feature:- Panel Self Refresh features PSR/PSR2, PR, Adaptive sync, and backlight control.

- Supports HDCP version 1.4, 2.2 and 2.3

- Supports Alternative Scrambler Seed Reset (ASSR)

- TPS4 with ASSR is supported

-

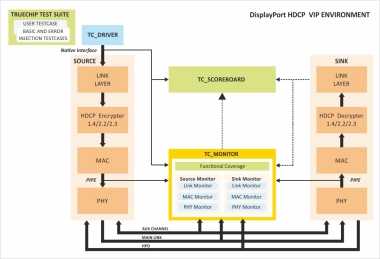

HDCP Verification IP

- Supports HDCP 1.4, HDCP 2.2 and HDCP 2.3 end to end protection.

- Can handle HDCP encryption and decryption for 8 bit and 32 bit link symbol.

- Capable of continuous link integrity check for all lanes and rates.

- Supports aux transactions for authentication protocol.

-

DisplayPort Transmitter IP

- Our 6th generation DisplayPort Transmitter Link Controller core supports DisplayPort 2.1, DisplayPort 1.4a and embedded DisplayPort 1.5.

- Features include link rates up to 20Gbps for DisplayPort 2.0, 8.1Gbps for DisplayPort 1.4a. Display Steam Compression (DSC), multi-stream transport (MST) and more. The base core includes all required link functionality— Main Link, Secondary Channel, and AUX Channel protocols—and supports the HDCP 2.3 standards for data encryption.

-

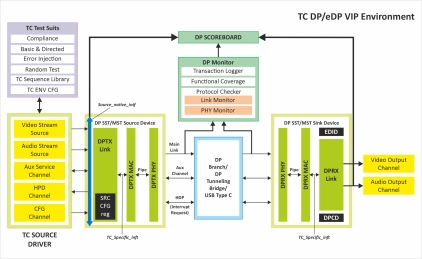

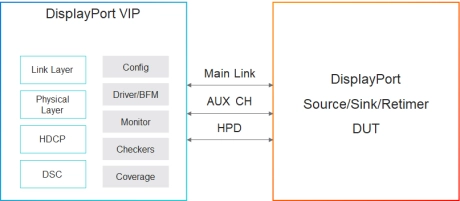

Simulation VIP for DisplayPort

- Device Support

- Source, Sink, Link Training-Tunable PHY Repeater (LTTPR/retimer)

- Main Link Interface

- Serial, Parallel (10-bit, 20-bit, 40-bit)

-

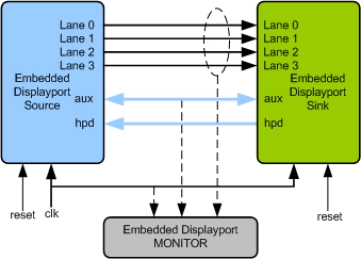

Embedded Display Port Verification IP

- Full Embedded Display port source device and sink device functionality.

- Embedded Display port v1.3,1.4,1.4b and 1.5 compliant and based on display port specs 1.2/1.2a/1.3/1.4/2.0.

- Support transmitter and receiver Mode.

- Supports multi lanes upto 4 lanes.

-

DisplayPort Receiver IP

- Silicon proven on multiple ASIC and FPGA processes

- Capable of operating without a host CPU in low complexity applications

- Horizontal and vertical video delimiter signals with 1, 2 or 4 pixels per output cycle, supporting up to 16K resolution output; deep color and HDR support

- 1.62 to 8.1 Gbps link rate across 1, 2, or 4 lanes