Z80 IP

Filter

Compare

7

IP

from

3

vendors

(1

-

7)

-

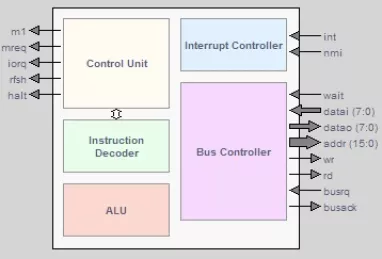

Advanced 8-bit microprocessor

- Fully compatible with Z80 industry standard

- Fully synthesizable, static synchronous de-sign with no internal tri-states

- No internal reset generator or gated clock

- Scan test ready

-

High-performance implementation of Z80/Z180 instruction set

- Full Z80/Z180 instruction set. Separate memory and I/O buses,

- optimized for direct connection to standard ASIC or FPGA

- memories and industry-standard peripheral functions. Separate

- interrupt vector bus for use with an optionaql external interrupt

-

Clean-room clone of Zilog Z8002 CPU

- Regular CISC architecture, with 16 general-purpose registers. 16-bit program counter. Includes 16x16 and 32x32 multiply as well as 64/32 and 32/16 divide.

-

Exact Copy of the Z80-SIO

- Technology-independent Verilog HDL implementation.

- 8-bit CPU interface.

- Two independent full-duplex channels.

- Receivers are quadruply buffered; transnmitters are doubly-buffered.

-

Rabbit (TM) 2000 microprocessor

- 8/16 bit CPU, four serial ports, five parallel ports, timers, real-time clock, and low-EMI features.

-

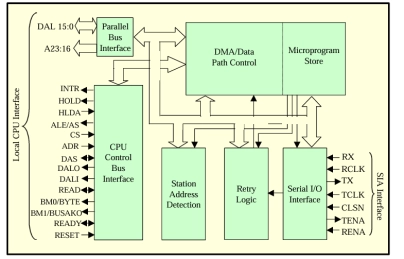

7990 Local Area Network Controller

- The SI79C90 Local Area Network Controller for Ethernet is an IP core designed to greatly simplify interfacing a microcomputer or minicomputer to an IEEE 802.3 / Ethernet Local Area Network.

- The SI 79C90 interfaces a minicomputer or microcomputer with the IEEE 802.3 / Ethernet Local Area Network. Its versatile bus interface logic interfaces the peripheral chip with Intel, Motorola, Zilog or AMD microprocessors.

-

Clean-room clone of Z180 TM CPU

- Fully functional synthesizable Verilog HDL model of the Z80180 TM CPU

- Vendor and technology independent

- Software compatible with several industry-standard processors

- 181 Instructions, plus an undefined opcode trap