XTS-AES IP

Filter

Compare

6

IP

from

3

vendors

(1

-

6)

-

XTS-AES IEEE P1619 Core Families

- Key Features Small size: XTS2-12.8 starts at less than 30,000 ASIC gates and delivers throughput of 7 Gbps. XTS3-18.2 starts at 44,000 ASIC gates at throughput of 18.2 bits per clock. The fastest cores in the families, XTS2-128 and XTS3-128, deliver 128 bits of throughput per clock (for example, at 500 MHz clock the maximum throughput is 64 Gbps).

- Completely self-contained: does not require external memory

- Supports both encryption and decryption

- Includes key expansion and CTS support

-

High Performance AES-XTS/ECB Core

- Scalable high-performance & low latency AES-XTS/ECB core with efficient support for varied networking traffic

- Standards compliant: NIST SP800-90-38E and IEEE Std 1619-2018

- Scalable throughput from 128 to 4096 bits/cycle (up to 4Tbps @ 1GHz)

- Encrypt/Decrypt/Bypass

-

High-Performance AES-XTS/ECB IP

- Scalable high-performance & low latency AES-XTS/ECB cores with efficient support for varied networking traffic

- Standards compliant: NIST SP800-90-38E and IEEE Std 1619-2018

- Two customer configurable IP cores with scalable throughput, 64 bits/cycle, 128 bits/cycle (up to 128 Gbps @ 1 GHz), 256 to 4096 bits/cycle (up to 4 Tbps @ 1 GHz)

- Encrypt/Decrypt/Bypass

-

AES Core XTS

- Complies with IEEE 1619-2007 and NIST SP800-38E standards

- Performance selectable to meet or exceed USB 3.0 and SATA 3.0 (6 Gbps), even on low cost FPGA families

- Low area, implementation of AES-XTS suitable for data storage applications.

- Based on the NIST validated (Cert #953) AES-G3 implementation of FIPS 197 (November 2001) Advanced Encryption Standard

-

P1619/802.1ae (MACSec) GCM/XEX/XTS-AES Core

- Small size: From 60K ASIC gates (at throughput of 18.2 bits per clock)

- 487 MHz frequency in 90 nm process

- Easily parallelizable to achieve higher throughputs

- Completely self-contained: does not require external memory. Includes encryption, decryption, key expansion and data interface

-

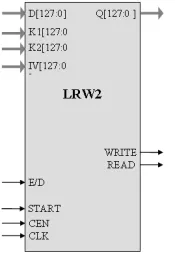

LRW-AES Core

- Small size: LRW1 starts at 30,000 ASIC gates at throughput of 12.8 bits per clock

- Synthesized for 600+ MHz clock speeds (70+ Gbps throughput for LRW2-128)

- Completely self-contained: does not require external memory

- Supports Liskov-Rivest-Wagner encryption and decryption (LRW-AES a.k.a. AES-LRW)