Universal Flash Storage IP

Filter

Compare

66

IP

from

8

vendors

(1

-

10)

-

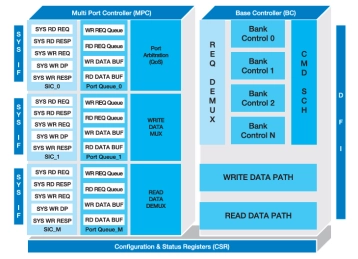

Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC Controller is a highly flexible and configurable design. It is targeted for high bandwidth access and low power consumption such as next generation mobile, DDR/LPDDR networking and consumer applications.

- The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities.

-

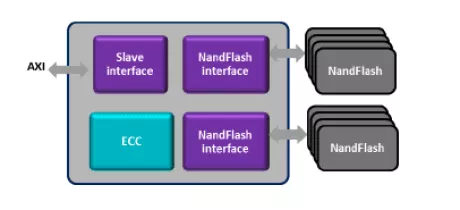

Universal NandFlash Controller

- The Universal NAND Flash Controller (IPM-UNFC) IP core is designed specifically to enable commodity Flash memory to be effectively used in enterprise storage applications requiring high reliability and large interconnect bandwidth.

- Using the pre-validated IPM-UNFC IP allows greatly reduced time-to-market for storage OEMs desiring higher IOPS benefitting from lower cost SLC, MLC , TLC & QLC NandFlash memory.

-

-

UFS Hardware Validation Platform (HVP)

- Compliant to JEDEC UFS 1.0, HCI 1.0, UniPro 1.40

- Available in Host and Device configuration

-

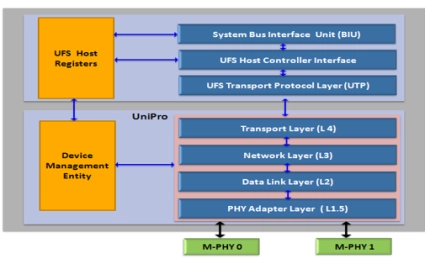

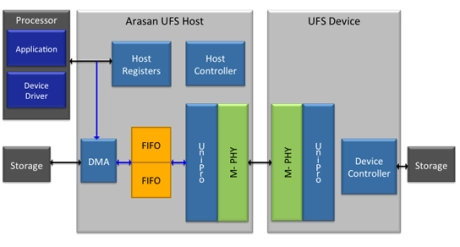

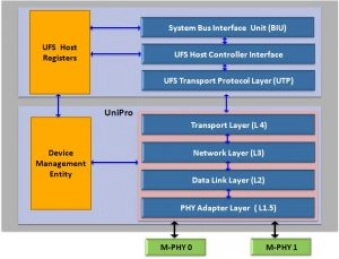

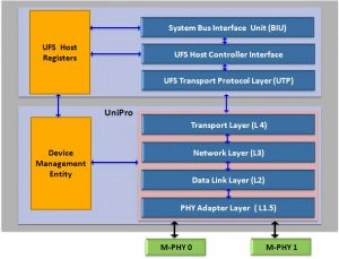

UFS 2.1 Host Controller IP

- JEDEC UFS 2.0 and UFS HCI 2.0 Compliant

- Supports high performance M-PHY v3.0 type-1

- 2 lanes @ 5.9 Gbps per lane

- UniPro v1.6 link layer

- Definable write-protect group size

-

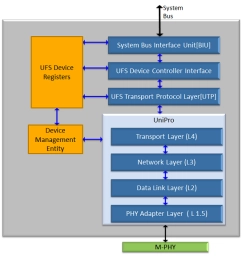

UFS 2.1 Device Controller IP

- The UFS 2.1 Device controller uses an M-PHY® 3.1 Adapter Layer backed by a UniPro v1.6 Link layer controller as per the specification.

- The UFS compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms.

-

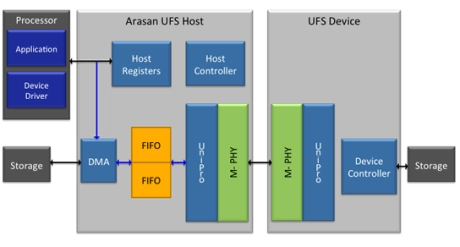

UFS 3.0 Host

- UFS 3.0 Host and Device configurations available

- Complete UFS 3.0 hardware implementation

- Interop-proven UniPro 1.8 link layer

- MIPI M-PHY 4.0 Interface

-

UFS 4.0 Host

- UFS 4.0 (JESD220F.pdf)

- UFS HCI 4.0 (JESD223E.pdf)

- MIPI UniPro version 2.0(mipi_UniPro_specification_v2-0.pdf)

- MIPI M-PHY version 5.0(mipi_M-PHY_specification_v5-0.pdf)

-

UFS 3.1 host

- The Universal Flash Storage 3.1 (UFS 3.1) is a simple but high-performance, serial interface primarily used in mobile systems, between host processing and nonvolatile eXecute-In-Place (XIP) or mass storage memory devices.

-

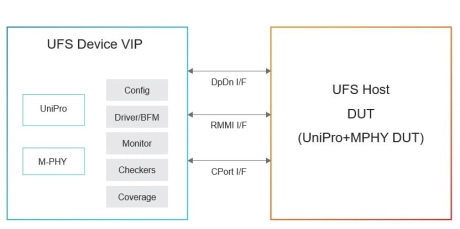

Simulation VIP for UFS

- Interfaces

- DPDN I/F and RMMI I/F when used with UniPro VIP. CPort signaling pin I/F and CPort message using transactions

- UTP Layer - UPIUs

- NOP IN, NOP OUT, Query Request/ Response, Task Management Request/ Response, Command, Response, Data Out, Data In