USB 3.2 IP

Filter

Compare

204

IP

from

28

vendors

(1

-

10)

-

USB 3.2 - Validates high-speed USB designs for protocol compliance and performance

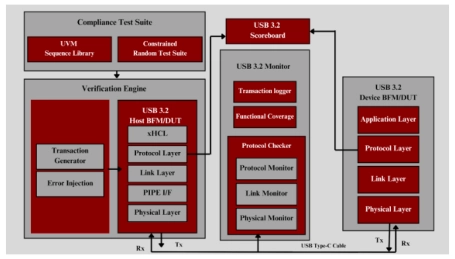

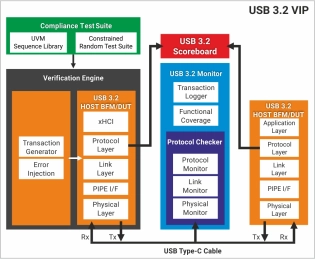

- XtremeSilica’s USB 3.2 Verification IP offers a comprehensive solution for validating designs based on the USB 3.2 specification. It supports SuperSpeed+ data rates up to 20 Gbps, ensuring protocol compliance, power management, and seamless interoperability across versions.

- The product’s advanced features include dynamic link negotiation validation, error injection, and robust debugging tools. It enables testing across a range of devices, ensuring high-speed data transfer and reliable performance in both legacy and modern USB designs

-

USB 3.2 Verification IP

- Fully compliant with USB 3.2 specification version 1.1, xHCI Specification Revision 1.2, and Pipe Interface 6.1.1 with Message Bus Interface for USB3.2 Architecture with backward compatibility to USB3.1, USB3.0 and USB2.0 (including USB2.0, USB 3.0. OTG)

- Supports USB Type-C.

- Supports up to 128 devices including hub and device on any tier level.

- Supports 15 IN and 15 OUT and 1 control endpoint for each device.

-

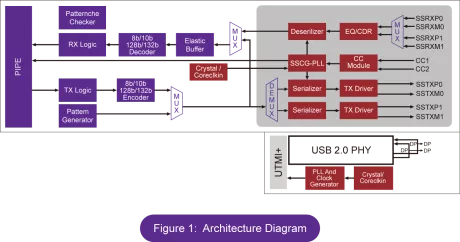

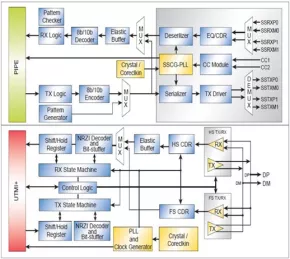

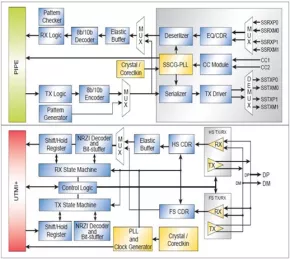

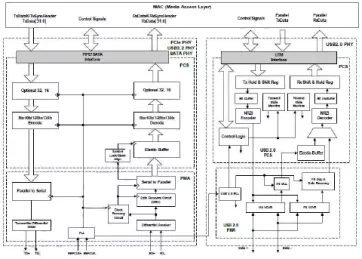

USB 3.2 Gen2x2 with PIPE 4.3 and USB2.0 with UTMI+ interface

- Fully compliant with USB 3.2 Gen2x1 featuring PIPE 4.3 and USB 2.0 with a UTMI+ interface

- Supports host, peripheral, and dual-role applications

- Supports 10/12/25/30/19.2/24/27/40 MHz crystal oscillators or clock inputs

- Supports TX 3-Tap FFE and RX CTLE+1-Tap DFE for SS+

-

USB 3.2 Gen2 PHY IP, Silicon Proven in TSMC 28HPC+

- Worldwide smallest USB 3.2 Gen2X1 PHY IP in 12/16nm process (IP size is smaller than 0.46mm²)

- Fully compliant with Universal Serial Bus (USB) 3.2 Gen2X1 and 2.0 electrical specifications

- Supports clock inputs from 25MHz crystal oscillator and external clock sources from the core

- Supports 3-Tap FIR Equalization for TX and CTLE+1-Tap DFE for RX

-

USB 3.2 Gen2 PHY IP, Silicon Proven in TSMC 16FFC

- Worldwide smallest USB 3.2 Gen2X1 PHY IP in 12/16nm process (IP size is smaller than 0.46mm²)

- Fully compliant with Universal Serial Bus (USB) 3.2 Gen2X1 and 2.0 electrical specifications

- Supports clock inputs from 25MHz crystal oscillator and external clock sources from the core

- Supports 3-Tap FIR Equalization for TX and CTLE+1-Tap DFE for RX

-

USB 3.2 Gen2 PHY IP, Silicon Proven in TSMC 12FFC

- Worldwide smallest USB 3.2 Gen2X1 PHY IP in 12/16nm process (IP size is smaller than 0.46mm²)

- Fully compliant with Universal Serial Bus (USB) 3.2 Gen2X1 and 2.0 electrical specifications

- Supports clock inputs from 25MHz crystal oscillator and external clock sources from the core

- Supports 3-Tap FIR Equalization for TX and CTLE+1-Tap DFE for RX

-

USB 3.2 Gen2 PHY IP, Silicon Proven in TSMC 7FF

- Worldwide smallest USB 3.2 Gen2X1 PHY IP in 12/16nm process (IP size is smaller than 0.46mm²)

- Fully compliant with Universal Serial Bus (USB) 3.2 Gen2X1 and 2.0 electrical specifications

- Supports clock inputs from 25MHz crystal oscillator and external clock sources from the core

- Supports 3-Tap FIR Equalization for TX and CTLE+1-Tap DFE for RX

-

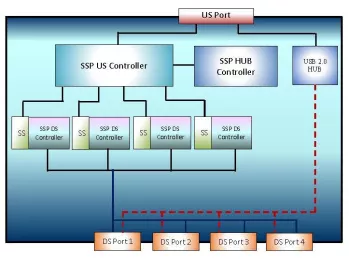

Super-Speed Plus USB 3.2 Hub Controller

- Supports two lanes or one lane - easily configurable

- Number of downstream ports can be easily selected

- Complies with USB 3.2 standard for Super-Speed Plus(10Gbps),Super-Speed(5.0 Gbps), Hi-Speed (480 Mbps), Full-Speed (12 Mbps) and Low-Speed (1.5 Mbps).

- Backward compatible with USB2.0 devices and hubs and the type A connectors.

-

USB 3.2/ PCIe 3.1/ SATA 3.2 Combo PHY IP, Silicon Proven in UMC 28HPC

- Compliant with PCIe 3.1 Base Specification

- Compliant with Universal Serial Bus 3.2 Specification

- Compliant with Universal Serial Bus 2.0 Specification

- Compliant with UTMI 1.05 Specification

-

USB 3.2 Gen2 PHY IP, Silicon Proven in UMC 28HPC

- Worldwide smallest USB 3.2 Gen2X1 PHY IP in 12/16nm process (IP size is smaller than 0.46mm²)

- Fully compliant with Universal Serial Bus (USB) 3.2 Gen2X1 and 2.0 electrical specifications

- Supports clock inputs from 25MHz crystal oscillator and external clock sources from the core

- Supports 3-Tap FIR Equalization for TX and CTLE+1-Tap DFE for RX