UCIe PHY IP

Filter

Compare

61

IP

from

18

vendors

(1

-

10)

-

UCIe PHY (Die-to-Die) IP

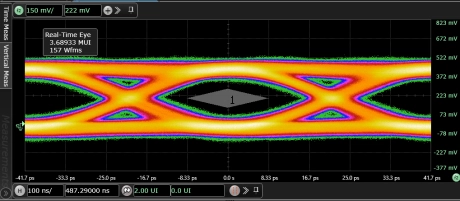

- Compliant with UCIe v2.0, supporting 4/8/12/16/24/32GT/s data rates

- for Standard Package up to 16 lanes / for Advanced Package up to 64 lanes

- Provides a 1024-bit data bus width with high-throughput die-to-die communication

- Includes automatic per-lane calibration and optional transmitter de-emphasis

-

-

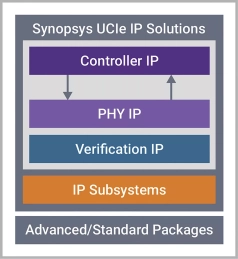

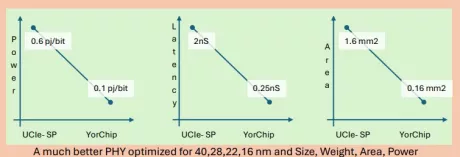

UCIe PHY & Controller

- Lightweight die-to-die interconnect solution consisting of the Physical Layer, Die-to-Die Layer and Protocol Layer optimized for highest performance with the lowest power and area overhead that is compliant to the Universal Chiplet Interconnect Express (UCIe) 2.0 specification.

-

UCIe Chiplet PHY & Controller

- Compliant with the UCIe specification (2.0 & 1.1)

- Flexible Structure, easy to customize (Pre-hardened PHY tuned to Customer Spec, PHY + Adapter Layer, PHY + Adapter Layer + Customized Protocol Layer)

- Supports the CXS/AXI using the streaming package (AXI Interface bandwidth up to 89%)

-

UCIe and BOW Universal PHY

- Novel Redundancy for Hi-Rel,

- Support for 16&18-bit wide data,

- Support Synchronous Operation,

- Supports Advanced packaging,

-

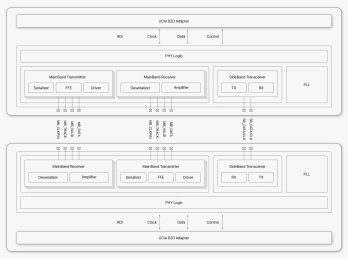

Universal Chiplet Interconnect Express PHY IP - GLOBALFOUNDRIES® 22FDX®

- Delivered as Hardmacro IP

- Implementation of the physical layer of the UCIe standard from Raw D2D Interface (RDI) to electrical interface of UCIe main band (MB) and sideband (SB)

- Includes TX and RX side

-

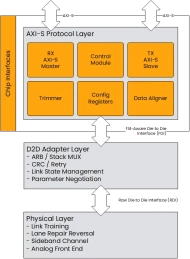

AXI-S Protocol Layer for UCIe

- Configurable Data width

- AXI4 Stream and AXI5 Stream Compliant

- All handshaking features including wakeup

- strb and keep for data flagging

-

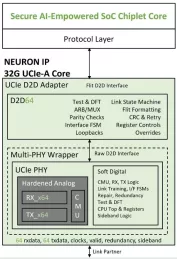

UCIe IP

- Supporting x16 link width with speeds up to 16 GT/s per lane, it conforms to UCIe’s standardized interface for seamless chiplet integration.

- Developed on GlobalFoundries 12LP+, this IP includes custom PHY, protocol, and die-to-die layers—engineered for performance, flexibility, and low latency.

-

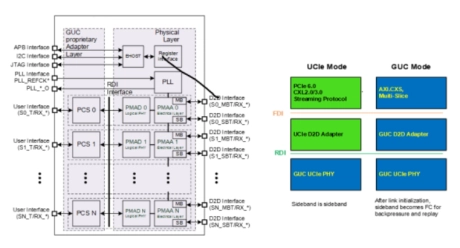

TSMC CLN5FF GUCIe LP Die-to-Die PHY

- IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face advanced package.

- This GUCIe PHY not only supports UCIe specification rev 1.1 compliance physical layer and Raw D2D interface (RDI) but also optionally provides the

-