UART IP

Filter

Compare

175

IP

from

55

vendors

(1

-

10)

-

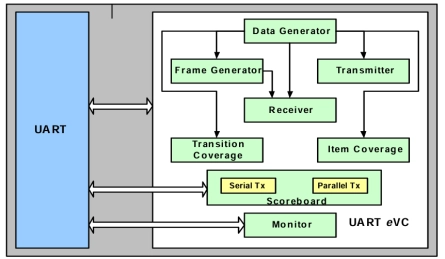

UART eVC

- UART eVC is a fully documented, off the shelf component for Cadence Specman Elite functional verification environment. At the heart of every asynchronous serial system is the Universal Asynchronous Receiver/Transmitter (UART).

- The UART is responsible for implementing the asynchronous communication process as both a transmitter and a receiver (both encoding and decoding data frames). The UART not only controls the transfer of data, but the speed at which communication takes place.

-

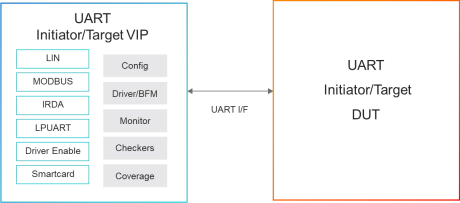

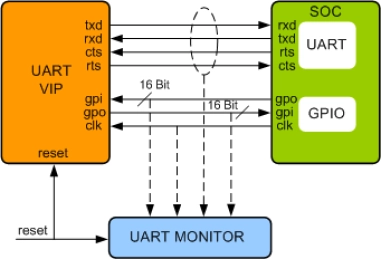

UART - Ensures reliable serial communication and protocol compliance in SoCs

- The UART Verification IP provides a comprehensive solution for validating UART communication interfaces in System-on-Chip (SoC) designs. It simulates both transmission and reception functionality to ensure data integrity. This IP supports error injection, debugging tools, and protocol compliance checking. It is ideal for ensuring reliability and protocol compliance in UART-based peripherals used in various applications, from simple devices to advanced systems.

-

-

UART Verification IP

- Fully compatible with 16550.

- Transmit and receive commands allow the user to transmit and receive UART data.

- Support additional functionality of IRDA, RS232, RS422, RS485 and GPIO.

- Configurable baud rate.

-

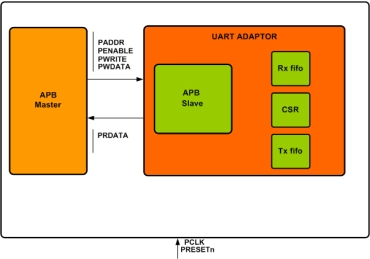

MIPI DEBUG UART Verification IP

- APB common support

- Supports different transfer types including IDLE, WRITE and READ.

- Supports unaligned address accesses.

- Slave memory map support.

-

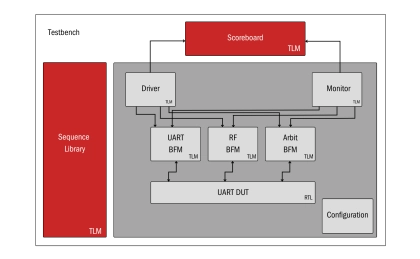

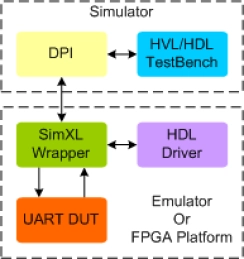

UART Synthesizable Transactor

- Fully compatible with 16550

- Supports transmit and receive commands allow the user to transmit and receive UART data

- Supports additional functionality of IRDA, RS232, RS422, RS485 and GPIO

- Supports full duplex operation

-

UART CONTROLLER IIP

- Implemented in Unencrypted Verilog, VHDL and SystemC

- Compliant with Standard UART 16550 Specification

- Full UART Functionality

- Transmit and receive commands allow the user to transmit and receive UART data

-

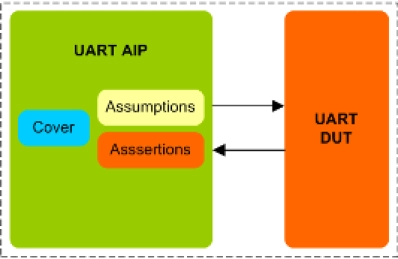

UART Assertion IP

- Specification Compliance

- Fully compatible with 16550.

- Transmit and receive commands allow the user to transmit and receive UART data.

- Support additional functionality of IRDA, RS232, RS422, RS485 and GPIO.

-

UART DO-254 IP Core

- The Universal Asynchronous Receiver/Transmitter (UART) is a hardware device that translates data between parallel and serial forms.

- UARTs are commonly used in conjunction with communication standards such as TIA (formerly EIA) RS-232, RS-422 or RS-485.

-

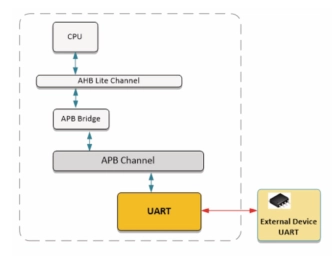

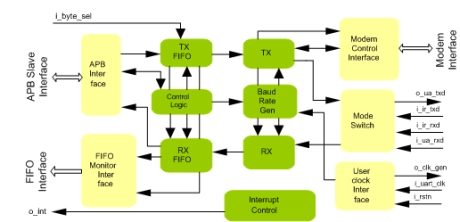

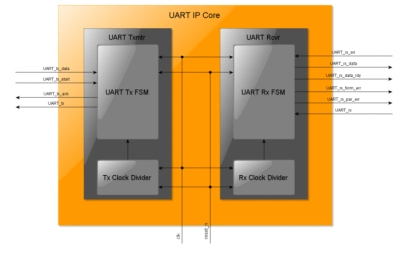

APB UART 16550

- This is a complete implementation of a 16550 UART.

- The UART contains the following main sections: Configuration Registers, Baud Rate, Generator, Transmitter, Receiver, Interrupt Generation Logic, Modem Control Logic