TileLink IP

Filter

Compare

218

IP

from

7

vendors

(1

-

10)

-

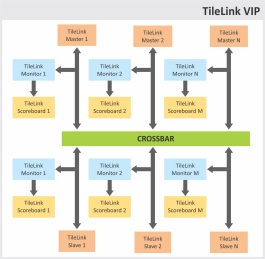

Simulation VIP for TileLink

- Channels

- Drive, sample, and check the signals and operations on channels A and D for TL-UL/TL-UH conformance level and on channels A, B, C, D and E for TL-C conformance level

- TL-UL

- Support for TL-UL conformance level including Flow Control Rules, Deadlock Freedom, Request-Response message ordering, Errors and Byte lanes

-

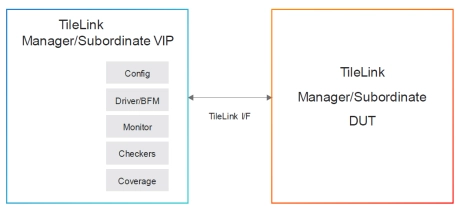

TileLink Verification IP

- Compliant with TileLink specification Version 1.8.1.

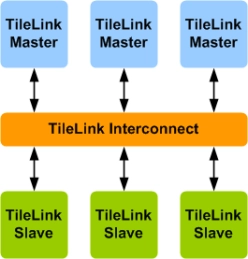

- Supports TileLink Master, TileLink Slave, TileLink Interconnect, TileLink Monitor and TileLink Checker.

- Supports TileLink Uncached Lightweight (TL-UL),TileLink Uncached Heavy weight (TL-UH) and TileLink Cached (TL-C) conformance levels.

- Supports Cache-coherent shared memory.

-

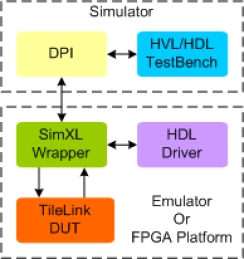

TileLink Synthesizable Transactor

- Compliant with TileLink specification Version 1.8.1.

- Supports TileLink Master, TileLink Slave and TileLink Interconnect.

- Supports TileLink Uncached Lightweight (TL-UL),TileLink Uncached Heavy weight (TL-UH) and TileLink Cached (TL-C) conformance levels.

- Supports Cache-coherent shared memory.

-

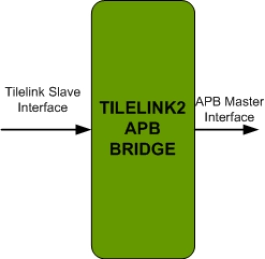

TileLink To APB Bridge IIP

- Compliant with SiFive TileLink specification version 1.8.1

- Compliant with AMBA APB3 , AMBA APB4 specification

- Translates Tilelink transactions into APB transactions

- Support for data phase timeout when APB interface does not send response

-

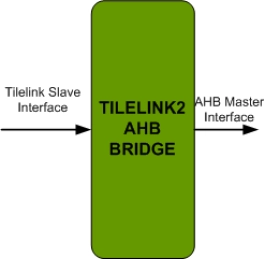

TileLink To AHB Bridge IIP

- Compliant with SiFive TileLink specification version 1.8.1

- Compliant with AMBA AHB specification

- Translates Tilelink transactions into AHB transactions

- Support for data phase timeout when AHB interface does not send response

-

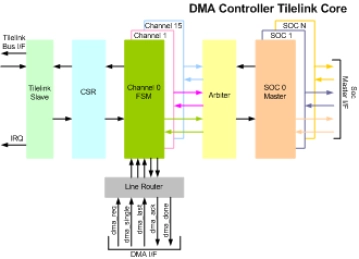

DMA Controller with TileLink IIP

- Supports 1-16 channel DMA Transmit and DMA Receive Engine

- Compliant with TileLink specification v1.7.1

- Supports access for Ring and Chained Descriptor Structures

- Configurable Transmit and Receive Engine based on Host Memory Data Width

-

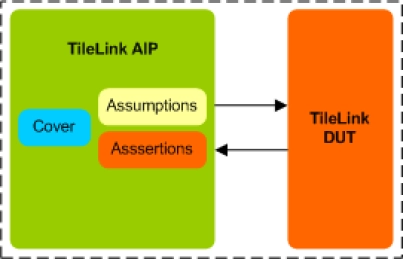

TileLink Assertion IP

- Specification Compliance

- Compliant with TileLink specification version 1.8.1.

- Supports TileLink Uncached Lightweight (TL-UL), TileLink uncached Heavy weight (TL-UH) and TileLink Cached (TL-C) conformance levels.

- Supports Cache-coherent shared memory.

-

TileLink Verification IP

- Compliant to TileLink specification from SiFive inc.

- Support for all type of TiLeLink Agents: TileLink Master, TileLink Slave

- Wide range of strict programmable protocol checks

- Slave memory data check

-

TileLink Target

- TL-UL both 1.7 and 1.8 standard

- TL-UL: 'PutFullData', 'PutPartialData', 'Get', 'AccessAck', 'AccessAckData' and Error response

- All three messages above, with and without latency transaction

-

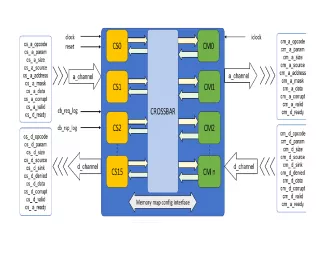

NoC Silicon IP for RISC-V based chips supporting the TileLink protocol

- Easy to integrate the NoC Silicon IP using interface

- N master and M slave ports based on customer requirement

- Supports wide range of memory map.