SDA OCT IP

-

SDA OCT Encoder and Decoder

- The SDA OCT Encoder handles the construction of Over-The-Air (OTA) frames as indicated in the standard, a preamble followed by a header and payload data, with both fields being protected by cyclic redundancy check (CRC) and forward error correction (FEC).

- The SDA OCT Decoder performs the synchronization of the Over-The-Air (OTA) frame and then decodes the header and payload data within the frame.

-

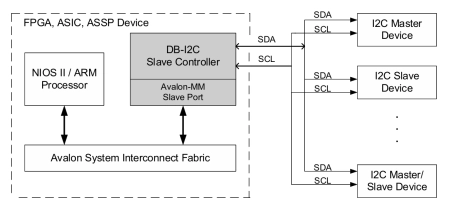

I2C Controller IP – Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-S-AHB Controller IP Core interfaces a NIOS II, ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the Avalon System Interconnect Fabric to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

-

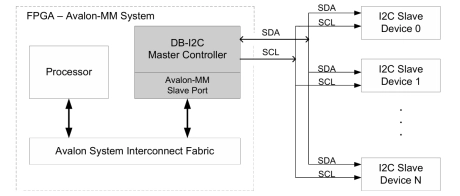

I2C Controller IP – Master, Parameterized FIFO, Avalon Bus

- The DB-I2C-M-AVLN Controller IP Core interfaces a microprocessor via the Avalon Bus to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-M-AVLN is a Master I2C Controller that controls the Transmit or Receive of data to or from slave I2C devices. In an Altera FPGA, typically, the microprocessor is a NIOS II processor, but can be any FPGA embedded processor. Figure 1 depicts the system view of the DB-I2C-M-AVLN Controller IP Core embedded within an FPGA integrated circuit device.

-

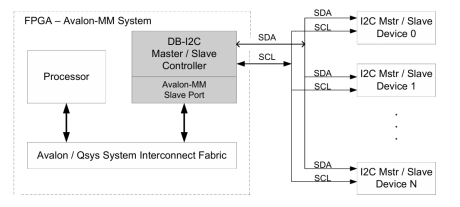

I2C Controller IP- Master / Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-MS-AVLN Controller IP Core interfaces a microprocessor via the Avalon Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-MS-AVLN is a Master / Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

I2C Controller IP – Slave, Parameterized FIFO, AHB Bus

-

The DB-I2C-S-AHB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 2.0/3.0 AHB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

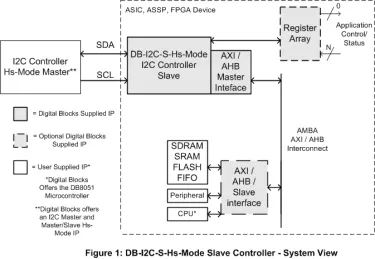

The DB-I2C-S-AHB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-AHB Controller IP Core embedded within an integrated circuit device.

-

-

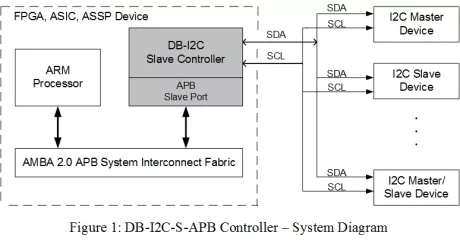

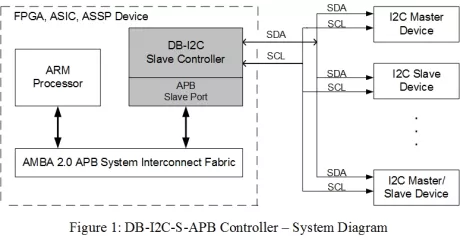

I2C Controller IP – Slave, Parameterized FIFO, APB Bus

- The DB-I2C-S-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high performance microprocessor via the AMBA 2.0 APB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

- The DB-I2C-S-APB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-APB Controller IP Core embedded within an integrated circuit device.

-

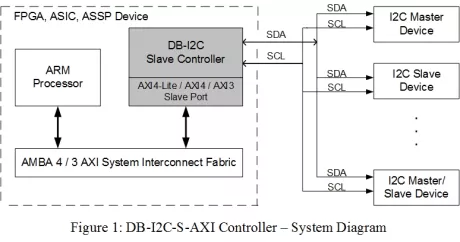

I2C Controller IP – Slave, Parameterized FIFO, AXI Bus

-

The DB-I2C-S-AXI Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 4/3 AXI System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-AXI is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-AXI Controller IP Core embedded within an integrated circuit device.

-

-

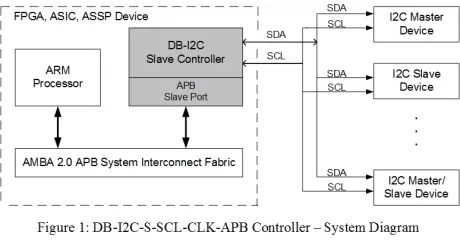

I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU

-

The DB-I2C-S-SCL-CLK-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 2.0 APB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-SCL-CLK-APB, in the I2C Slave Controller Core managing the I2C protocol & physical layer, contains no free running clock, while interfacing through dual clock FIFOs to the AMBA APB Bus, for a low power, low noise Microprocessor interface to the I2C Bus. The I2C Slave Controller Core runs off the external SCL clock while the APB side off the APB Clock.

-

-

I2C Controller IP – Slave, Parameterized FIFO, Hs-Mode (3.4 Mbps) AXI/AHB/APB/Avalon Buses or direct to/from Registers or Memory

- The DB-I2C-S-Hs-Mode I2C Slave Controller IP Core interfaces user Registers to an I2C Bus or Memory (SDRAM / SRAM / Flash / FIFO) or any Peripheral or CPU connecting through an internal AHB / APB / AXI / Avalon / Qsys Bus to an I2C Bus in Hs-Mode (3.4 Mbit/s) / Fast-Mode Plus (1 Mbit/s) / Fast-Mode (400 Kbit/s) / Standard-Mode (100 Kbit/s).

- The DB-I2C-S-Hs-Mode Controller implements the Slave-Transmit and Slave-Receive protocol according to the Philips I2C-Bus Specification, Version 2.1 as well as the updated NXP Rev 7 – 1 Oct 2021 Specification.

-

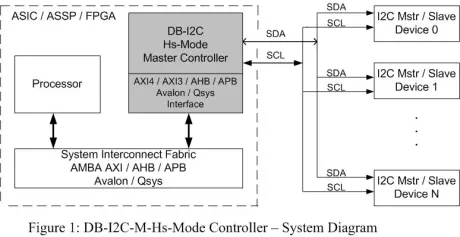

I2C Controller IP – Master, Parameterized FIFO, Hs-Mode (3.4 Mbps) AXI/AHB/APB/Avalon Buses

- The DB-I2C-M-Hs-Mode Controller IP Core interfaces a microprocessor via the AMBA AXI / AHB / APB Bus or Avalon Bus to an I2C Bus in Hs-Mode (3.4 Mbit/s) / Fast-Mode Plus (1 Mbit/s) / Fast-Mode (400 Kbit/s) / Standard-Mode (100 Kbit/s). The DB-I2C-M-Hs-Mode Controller IP Core can also interface a set of Registers within an ASIC / ASSP / FPGA device as well as interface Memory (e.g. SDRAM / SRAM / FLASH) to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.