RapidIO 3.1 IP

Filter

Compare

9

IP

from

5

vendors

(1

-

9)

-

RapidIO Verification IP (VIP)

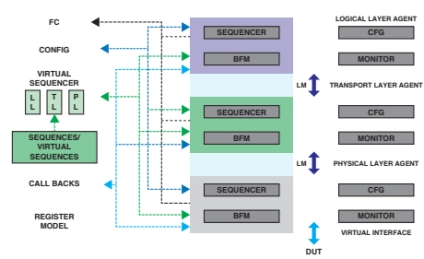

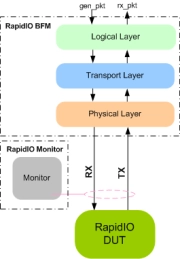

- The RapidIO Verification IP (VIP) provides highly capable compliance verification solution for the RapidIO protocol.

- The RapidIO VIP is system Verilog (SV) based and supports standard Universal Verification Methodology (UVM).

- It can be easily combined with any other UVM compliant verification components to extend a broader verification environment.

-

RapidIO Verification IP

- Supports RapidIO specification 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1.

- Supports Serial 1x/2x/4x/8x and 16x Physical lanes.

- Supports 8b/10b and 64b/67b Encode and Decode functions.

- Supports scrambler/Descrambler.

-

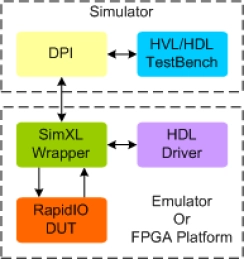

RapidIO Synthesizable Transactor

- Supports RapidIO specification 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1.

- Supports Serial 1x/2x/4x/8x and 16x Physical lanes.

- Supports 25.78125Gbaud/s, 12.5Gbaud/s, 10.3125Gbaud/s, 6.25Gbaud/s, 5Gbaud/s,3.125 Gbaud/s, 2.5 Gbaud/s, 1.25 Gbaud/s.

- 8b/10b Encode and Decode functions.

-

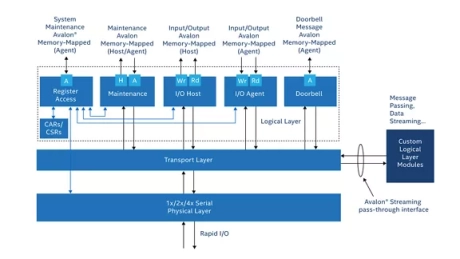

RapidIO Intel® FPGA IP

- Intel is discontinuing the intellectual property (IP) for RapidIO I and RapidIO II, more information can be found in the product discontinuance notification (PDN2025).

-

RAPIDIO EndPoint Controller IIP

- Compliant with RapidIO Interconnect 2.2 specification

- Supports all Capability Registers(CARs) and Configuration and Status Registers(CSRs)

- Supports high link utilization and low latency

- Supports efficient receive and transmit buffering scheme

-

LogiCORE IP Serial RapidIO Gen 2

- 1x, 2x, & 4x Serial PHY - supports Artix-7, Kintex-7, Zynq-7000, Virtex-7, and Virtex-6 FPGAs

- 1x, 2x & 4x Serial PHY - supports 1.25, 2.5, 3.125, 5.0, and 6.25 Gbps line speed

- Supports IDLE1 and IDLE2 sequence

- Supports Packet Retry, stomp, transmission error recovery, throttle-based flow control and CRC

-

Serial RapidIO LogiCORE IP

- 1x & 4x Serial PHY - Supports Virtex-6 LXT/SXT/HXT, Spartan-6 LXT, Virtex-5 LXT/SXT/FXT, and Virtex-4 FX FPGAs

- 1x & 4x Serial PHY - Supports 1.25, 2.5, 3.125, 5.0 Gpbs line speed

- 1x & 4x Serial PHY - 64-bit internal data path

- Supports Packet Retry, stomp, transmission error recovery, throttle-based flow control and CRC

-

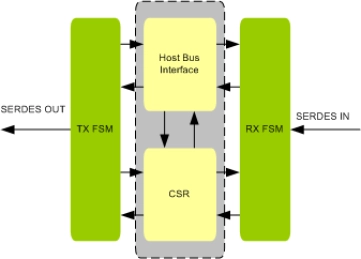

Serial RapidIO Controller

- Fully compliant with the RapidIO specification revision 2.2,

- Simple transaction interface with Host processor and DMA Engine,

- Configurable FIFOs implemented by BlockRAM in both transmit and receive paths,

- Register file containing all necessary architectural registers providing total software control of IP core,

-

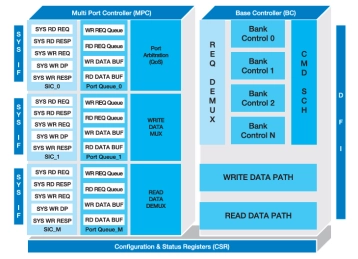

Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC Controller is a highly flexible and configurable design. It is targeted for high bandwidth access and low power consumption such as next generation mobile, DDR/LPDDR networking and consumer applications.

- The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities.