PCIe Switch IP

Filter

Compare

124

IP

from

17

vendors

(1

-

10)

-

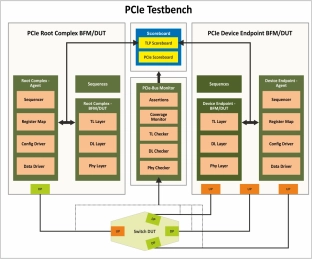

PCIe Switch Verification IP

- Compliant with the PCIe 6,5,4,3 specification.

- Support Pipe Specification 6.1.1

- NVMe on top of Low Power, CXS, CPI, CXL, CXL Security, PCIe Gen6/5/4/3 management

- Supports Pipe Specification 6.1 with both Low Pin Count and Serdes Architecture.

-

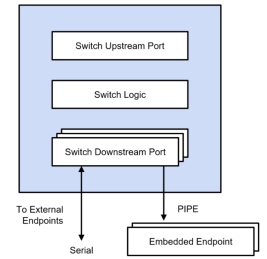

PCIe Switch for USB4

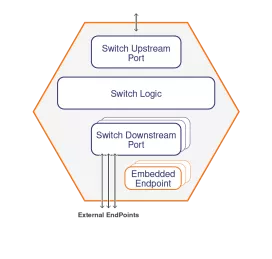

- Fully transparent design eliminates the need for Host configuration and management software

- Built-in support for PIPE-attached embedded endpoints (including 64-bit PIPE) for reduced BoM, latency, and power

- Seamless implementation on ASIC and FPGA with same RTL code base, up to x8 Gen4 per port on FPGA (or x16 Gen3)

- Lowest latency switching logic on the market (2 clock cycles)

-

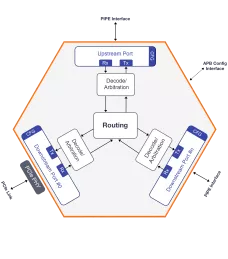

PCIe 6.2 Switch

- 1 upstream port, up to 7 downstream ports

- Up to 128 lanes

- PCIe TLP routing: Configuration, Memory Write/Read, I/O and Messages Packets

- L1 and wake-up events forwarding

-

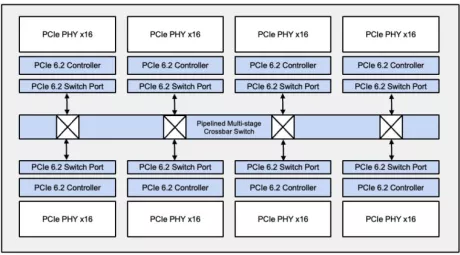

PCIe 7.0 Switch

- Configurable from PCIe 7.0 x8/ PCIe6x16 @1GHz clock down to PCIe 5.0 x1

- Highly scalable with up to 31 configurable external or embedded endpoints

- Configurable Egress Buffer for non-blocking output queueing switch performance

- Flit mode to non-Flit mode conversion

- Low power optimized

- Superior performance through a nonblocking architecture

- Minimized footprint

-

PCIe 5.0 Multi-port Switch

- Fully transparent design eliminates the need for Host configuration and management software

- Built-in support for PIPE-attached embedded endpoints (including 64-bit PIPE) for reduced BoM, latency, and power

- Seamless implementation on ASIC and FPGA with same RTL code base, up to x8 Gen4 per port on FPGA (or x16 Gen3)

- Lowest latency switching logic on the market (2 clock cycles)

-

Automotive-grade controllers for PCIe 2.0/1.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

Configurable controllers for PCIe 6.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

Configurable controllers for PCIe 5.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

Configurable controllers for PCIe 4.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

Configurable controllers for PCIe 3.1 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility