PCIe DMA Controller IP

Filter

Compare

44

IP

from

17

vendors

(1

-

10)

-

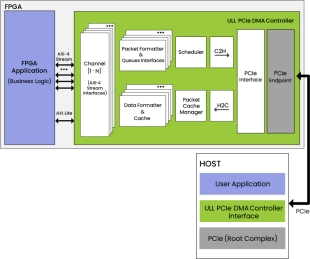

ULL PCIe DMA Controller

- The ULL PCIe DMA Controller is a high-performance, bidirectional data transfer solution. It is designed for seamless communication between FPGAs and host CPUs over PCIe.

- With a round-trip time as low as 585ns*, this IP core empowers developers to maximize resource utilization and achieve ultra-low latency without compromising performance.

-

PCIe DMA Controller (Low Latency)

- Implements standard Transaction layer functions e.g. TLP generation/reception, TLP completion handling and interrupt generation

- Implements 32-bit, 64-bit, 128-bit and 256-bit User application. (Width selection is based on PCIe endpoint interface width)

- PCIe Gen1, Gen2 and Gen3 support.

- Up to 8 independent DMA channels with each channel capable of operating in Block-DMA or Scatter-Gather DMA modes

-

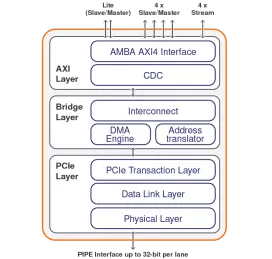

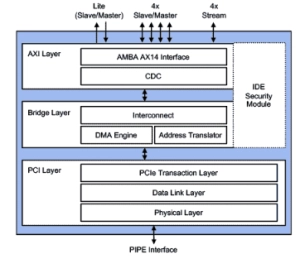

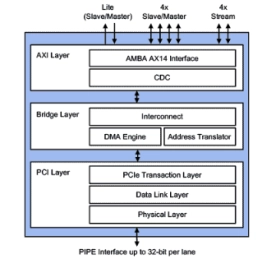

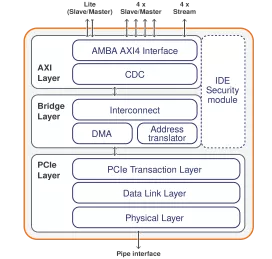

PCIe 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- PCIe Interface

- Supported silicon:

- AMBA AXI Interface

- Data Engine and Address translation for PCIe-to-AXI and AXI-to-PCIe transfers

-

PCIe Controller for USB4 with AXI

- Internal data path size automatically scales up or down (64-, 256-, 512- bits) based on link max. speed and width for reduced gate count and optimal throughput

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs up to Gen4 x8/Gen3 x16 with same RTL code – Gen5 support pending

- Stringent implementation of PCIe to AXI Ordering Rules and AXI to PCIe Ordering Rules guarantees AXI deadlock prevention

- Carefully engineered AXI bridge & AXI interconnect allows full performance on AXI interfaces

-

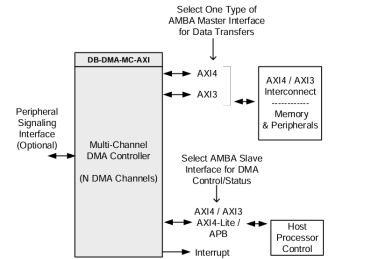

SG DMA Controller, 1-16 DMA Channels, AXI4 / AXI3 Master Interfaces

- The DB-DMAC-MC-AXI Verilog RTL IP Core is a Multi-Channel DMA Controller supporting 1 – 16 independent data transfers.

- The Direct Memory Access (DMA) Controller IP Core contains 1 - 16 DMA Controller Engines (i.e. DMA Channels), with user selectable AMBA AXI4 / AXI3 Master Read/Write interconnects.

- The DB-DMAC-MC-AXI excels at high data throughput on both small and large data sets. Standard IP releases of number of DMA Controller Engines are 1, 2, 4, 8, 16.

-

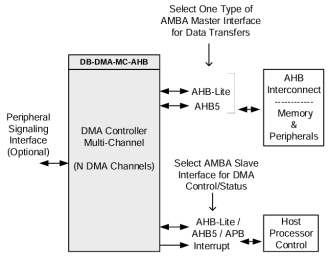

SG DMA Controller, 1-16 DMA Channels, AHB5 Master Interface

- The DB-DMAC-MC-AHB5 & DB-DMAC-MC-AHB-Lite Verilog RTL IP Core is a Multi-Channel DMA Controller supporting 1 – 16 independent data transfers.

- The Direct Memory Access (DMA) Controller IP Core contains 1 - 16 DMA Controller Engines (i.e. DMA Channels), with a unified AHB Master Read/Write interconnects.

- The DB-DMAC-MC-AHB excels at high data throughput on both small and large data sets. Standard IP releases of number of DMA Controller Engines are 1, 2, 4, 8, and 16.

-

PCIe Controller Testbench

- Emulates a Root Complex device enabling simulation of a PCI Express design

- Test scripts are used to generate Root Complex master requests

- Automatically responds to DUT master requests

- Performs automatic data logging and checking

-

PCIe 2.1 Controller with AXI

- PCIe Interface

- Supported silicon:

- AMBA AXI Interface

- Data Engine and Address translation for PCIe-to-AXI and AXI-to-PCIe transfers

-

PCIe 5.0 Controller with AXI

- Comprises complete PCIe 5.0 interface subsystem with Rambus PCIe 5.0 PHY

- Supports the PCI Express 5.0 rev. 1.0 (32 GT/s), 4.0 (16 GT/s), 3.1/3.0 (8 GT/s) and PIPE (8, 16, 32 and 64-bit) specifications

- Supports the PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

-

PCIe 4.0 Controller with AXI

- Internal data path size automatically scales up or down (64-, 256- bits) based on link max. speed and width for reduced gate count and optimal throughput

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs up to Gen4 x8/Gen3 x16 with same RTL code

- Stringent implementation of PCIe to AXI Ordering Rules and AXI to PCIe Ordering Rules guarantees AXI deadlock prevention

- Carefully engineered AXI bridge & AXI interconnect allows full performance on AXI interfaces