PCI Express 5.0 IP

Filter

Compare

288

IP

from

22

vendors

(1

-

10)

-

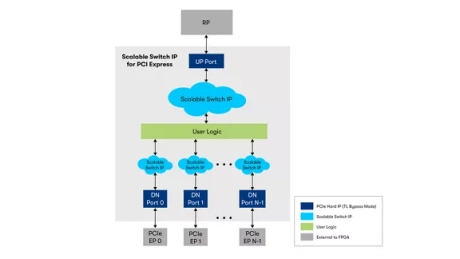

Scalable Switch Intel® FPGA IP for PCI Express

- The Scalable Switch Intel® FPGA IP for PCI Express is a fully configurable switch that implements one fully configurable upstream port and connectivity for up to 64 downstream ports.

-

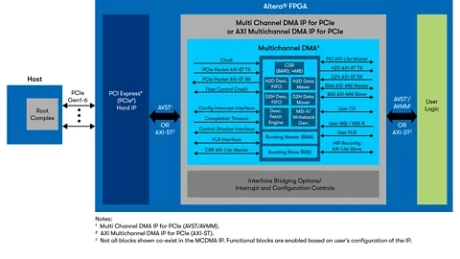

Multichannel DMA Intel FPGA IP for PCI Express*

- The Multichannel DMA IP for PCI Express provides high efficiency, speed, and configuration flexibility to support various applications from HPC, cloud, networking, to embedded

- With support for up to 2048 channels and Linux-based PCIe drivers provided, this low latency, low resource utilization solution is essential in handling movements of large volumes of data to optimize system performance.

-

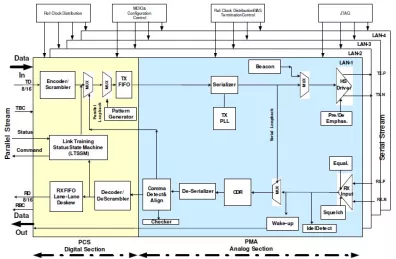

PCI Express Gen5 SERDES PHY on Samsung 8LPP

- Industry leading low power PMA macro – 224mW per lane at 28Gbps (8.0 mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.38 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

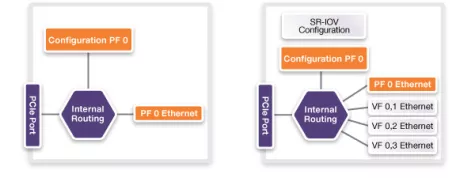

Multi-Port Switch IP for PCI Express

- Designed according to the PCI Express 4.0, 3.1, 2.1, and 1.1 specifications, including the latest errata

- Designed according to the PCI-SIG Single-Root I/O Virtualization specification

- Supports PIPE PHY interface definition including variable clock and variable data

- Supports 16.0, 8.0, 5.0 and 2.5 Gbps line rates

-

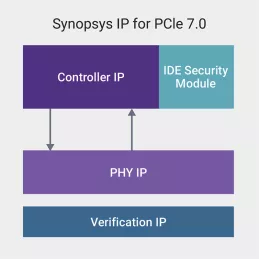

IDE Security IP Modules for PCI Express 7.0

- Full support of PCI Express 7.0 (64GT/s) IDE specification

- High-performance AES-GCM based packet encryption, decryption, authentication

- Seamless integration with Synopsys controllers via TLP/FLIT packet-based interface

- FLIT mode support

- Support for PCIe 7.0, 6.0, 5.0, 4.0 and 3.1 data rates

-

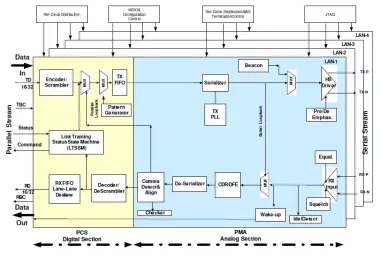

PCI Express PHY

- Quad PCIe 16/8/5/2.5 Gbps per lane

- Tight control over termination resistor (~50 Ohm) with on chip calibration

- Tight skew control of 1UI between lanes of the PMA

- 3-tap Tx Finite Impulse Response (FIR) equalizer with multi-level de-emphasis

-

PCI Express Gen 1/2/3/4 Phy

- TSMC advanced 16 nm FFC CMOS process

- Available in 1X, 4X, 8X, and 16X configuration

-

PCI Express Gen 1/2/3/4 Phy

- 2.5/5.0/8/16 Gbps per lane interface optimized for PCI Express applications

- Compliance to PCI Express 1.0a, 1.1 and 2.1, 3.1 and 4.0 PIPE specifications

-

UltraScale+ Device Integrated Block for PCI Express (PCIe)

- Designed to PCI Express Base Specification 3.1

- PCI Express Endpoint, Legacy Endpoint or Root Port Port Modes

- x1, x2, x4, x8 or x16 link widths

- Gen1, Gen2 and Gen3 link speeds

-

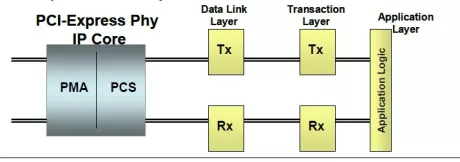

PCI Express Gen 1/Gen 2 Phy

- 2.5/5.0 Gbps per lane interface optimized for PCI Express applications

- Conforms to PCI Express Specification 1.0a, 1.1 and 2.0

- PIPE compliant parallel interface