LPDDR3 SDRAM IP

Filter

Compare

54

IP

from

5

vendors

(1

-

10)

-

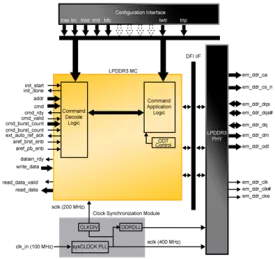

LPDDR3 SDRAM Controller

- Interfaces to Industry Standard LPDDR3 SDRAM components and modules compliant with the JESD-209.3 specification

- High-Performance LPDDR3 performance, up to 400 MHz/800 Mbps operation

- Supports automatic LPDDR3 SDRAM initialization and refresh

- Supports Deep Power Down Mode

-

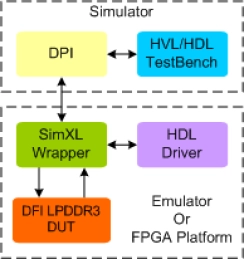

LPDDR3 DFI Synthesizable Transactor

- Compliant with DFI version 3.1 or higher Specifications.

- Supports LPDDR3 devices compliant with JEDEC LPDDR3 SDRAM Standard JESD209-3.pdf, JESD209-3B.pdf and JESD209-3C.pdf

- Supports for Read data-eye training.

- Supports for Read gate training.

-

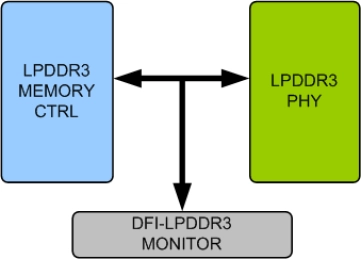

LPDDR3 DFI Verification IP

- Compliant with DFI version 3.1 or higher Specifications.

- Supports LPDDR3 devices compliant with JEDEC LPDDR3 SDRAM Standard JESD209-3.pdf, JESD209-3B.pdf and JESD209-3C.pdf

- Supports for Read data-eye training

- Supports for Read gate training

-

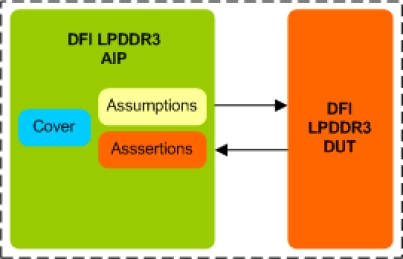

LPDDR3 DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 3.1 or higher Specifications.

- Supports LPDDR3 devices compliant with JEDEC LPDDR3 SDRAM Standard JESD209-3.pdf, JESD209-3B.pdf and JESD209-3C.pdf.

- Supports for Read data-eye training.

-

Performance Enhanced version of uMCTL2 supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3 and LPDDR2 for Automotive

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

Performance Enhanced version of DDR Enhanced Memory Ctl (uMCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

DDR Enhanced Protocol Controller (uPCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

DDR4 multiPHY SP - SS 14LPP

- Support for JEDEC standard DDR4, DDR3, LPDDR2, and LPDDR3 SDRAMs

- Scalable architecture that supports data rates up to DDR4-2667

- Support for DIMMs

- Delivery of product as a hardened mixed-signal macrocell component allows precise control of timing critical delay and skew paths

-

DDR4 multiPHY - UMC 28HPC18

- Support for JEDEC standard DDR4, DDR3, LPDDR2, and LPDDR3 SDRAMs

- Scalable architecture that supports data rates up to DDR4-2667

- Support for DIMMs

- Delivery of product as a hardened mixed-signal macrocell component allows precise control of timing critical delay and skew paths

-

DDR4 multiPHY - TSMC 28HPC+18

- Support for JEDEC standard DDR4, DDR3, LPDDR2, and LPDDR3 SDRAMs

- Scalable architecture that supports data rates up to DDR4-2667

- Support for DIMMs

- Delivery of product as a hardened mixed-signal macrocell component allows precise control of timing critical delay and skew paths